## Pinging for Distant and Delayed Topologies

#### An Open Discussion

Jerry Hauck Dave LaFollette

# Goal

As implemented today, 1394 devices assume topologies restricted to 4.5 m cable lengths and PHY\_DELAY less than 144 nSec. Two factors are already challenging these assumptions:

- <u>In-Home Network</u>: Longer cable runs are an absolute must for home theater or intra-room wiring.

- <u>P1394b</u>: "Beta" mode may require larger PHY delays to accommodate symbol encoding/decoding.

# ⇒ P1394a must provide a seemless path to distant or delayed topologies.

#### How to set Gap Count

- The basic challenge to distant or delayed topologies is proper setting of the gap count:

- Current table-based approaches are inherenlty built on constrained topology assumptions and simply map the number of hops from root onto an appropriate gap count. The tables yield incorrect values for longer cables or slower PHY's.

- Gap count *could* be fixed at maximum of 63, but will likely result in unneessary degradation in bus efficiency.

- "PHY pinging" has been suggested as one mechanism to dynamically set an optimal gap count.

# Phy Pinging

- A simple concept, pinging returns the roundtrip delay between any two devices by measuring the elapsed time (at the first device) between the launch of a ping request and the reception of a ping acknowledge from the second device.

- A specialized "ping timer" is required in hardware to accurately measure the round trip delay. Two basic ping methods can be considered:

- Ping timer in every node

- Single ping timer in the bus manager

#### A Note About Jitter

- Jitter introduced by reclocking in a PHY can add considerably to the uncertainty of the ping timer. This uncertainty accumulates as the ping path covers more hops.

- Since the jitter due to reclocking can be anticipated, statistical averaging techniques could be employed to isolate the deterministic delay from the jitter. For the purposes of this discussion, it is assumed that jitter has been removed from the measured values.

### Ping Timer in All Nodes

- Gap count is selected by:

- Ping from "leaf to leaf" (all leaf nodes to all other leaf nodes)

- Largest ping timer value represents worst case round-trip delay plus time fore responder to form an acknowledge

- Subtract minimum response time from worst-case path and use result to set proper gap count

- Remote pinging rather than higher-layer protocols can be used to command leaf nodes to ping but requires additional silicon.

- All topologies are easily analyzed, but costs a timer in each and every node.

### Single Timer in Bus Manager

- A single timer in the bus manager can achieve similar results IF additional PHY information is available.

- The bus manager needs to know each PHY's worst-case PHY\_DELAY in order to properly reconstruct ping paths.

- Consider each leaf-to-leaf path and note that the bus manager can either be "on" or "off" of the path ...

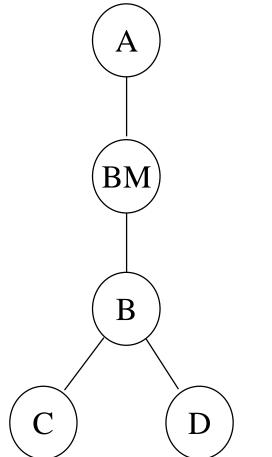

# Single Ping Timer Method

#### • "On the Path"

Roundtrip from A to C can be approximated by:

$$\label{eq:ping} \begin{split} Ping(A \ to \ C) &= Ping \ (A \ to \ BM) + Ping \ (BM \ to \ C) + \\ & \mathbf{2*PHY\_DELAY(BM)} \end{split}$$

#### • "Off the Path"

Roundtrip from C to D can be approximated by:

$\begin{aligned} \text{Ping}(\text{C to } \text{D}) &= \text{Ping} (\text{BM to } \text{C}) + \text{Ping} (\text{BM to } \text{D}) - \\ 2^*\text{Ping}(\text{BM to } \text{B}) - 2^*\text{PHY}_\text{DELAY}(\text{B}) \end{aligned}$

# Reporting Actual PHY\_DELAY

- Actual PHY\_Delay is required for the single timer method and could be specified in the self-id "caboose"?

- The theoretical limit of PHY\_Delay is 31, half of the maximum gap count

- Actual PHY\_Delay can be reported in units of gap count fractions over the nominal delay of 144 nSec. 8 bits covers the maximum range and has precision that would yield overly conservative gap counts 12.5% of the time. Fewer bits can be specified by restricting the maximum PHY\_DELAY or sacrificing precision.

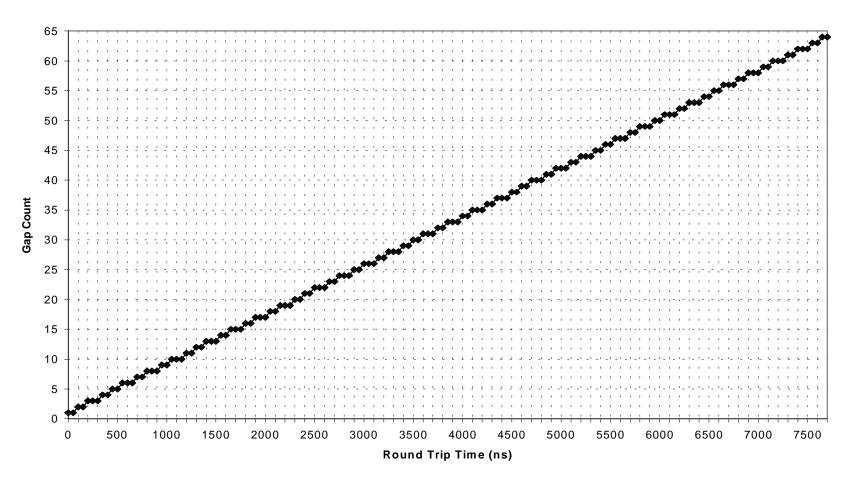

#### Gap Count vs Round Trip Delay

Gap Count vs. Round Trip time

Copyright & Permissions: Intel Corporation

04/12/97

#### Timer Location

- For the single timer method, it may be desirable to locate the ping timer in the link. This allows all PHY's to be identical, and places the ping burden only on the bus manager's link layer.

- To put the timer in the link, a tight min/max range spec on the PHY/LINK latency would be required to eliminate additional jitter.

## Summary

- 1394 must support longer distance and slower PHY's to be adopted in the home and to ensure the viability of P1394b

- PHY pinging offers one known solution to dynamically calculate appropriate gap counts.

- Remote PHY pinging provides the most direct calculation but burdens all devices with ping timer.

- PHY pinging with a single timer is possible, but requires dynamic reporting of actual worst case PHY delay.

- Ping timer can be placed in the link if the PHY to link latency is well specified with a small maximum to minimum range.