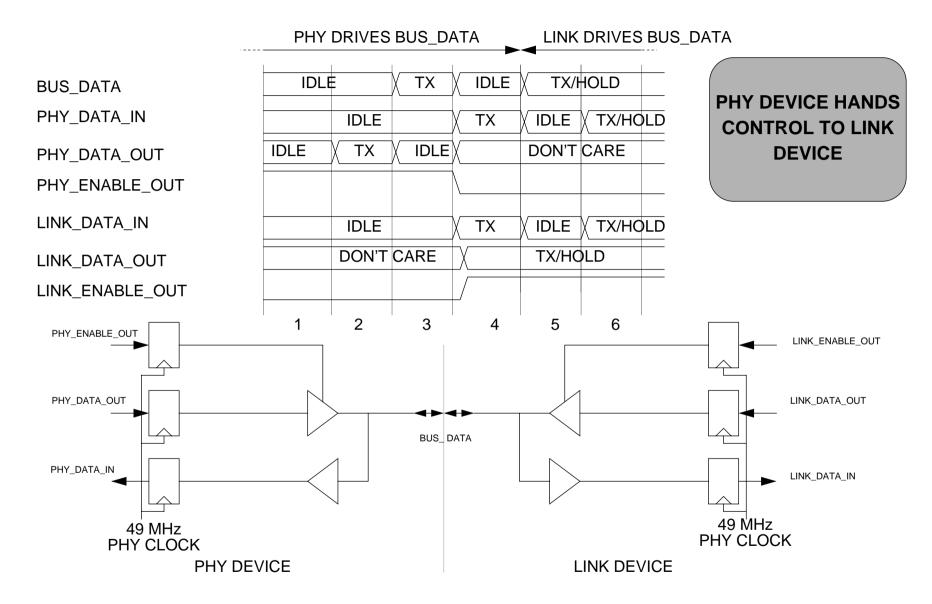

# Description of Interface Behaviour for the PHY device handing control to the Link device to allow packet transmission

## Cycle 1

PHY device is arbitrating on the 1394 bus for a previous Link request for transmission.

# Cycle 2

PHY device has won arbitration on the 1394 bus. It internally asserts TX on its internal CTL lines (PHY\_DATA\_OUT) to indicate this to the Link.

## Cycle 3

The PHY device's TX indication is now visible on the PHY-Link bus (BUS\_DATA). In this same cycle the PHY device drives IDLE onto its internal CTL lines (PHY\_DATA\_OUT)

#### Cycle 4

The PHY device now hands control over to the Link. It de-asserts its internal PHY\_ENABLE\_OUT, and can now drive any value on its internal PHY\_DATA\_OUT lines. Note that the PHY device is still driving the BUS\_DATA bus during this cycle since the PHY\_ENABLE\_OUT signal is registered.

The Link 'sees' the PHY device's indication of TX during this cycle (LINK\_DATA\_IN). Turning around within the same cycle, it immediately drives its own LINK\_ENABLE\_OUT, and drives TX/HOLD on its LINK\_DATA\_OUT. Note that the Link cannot drive IDLE during this cycle onto BUS\_DATA, since its output path is registered.

## Cycle 5

The bus turnaround occurs within this cycle. The PHY device has de-asserted its tristate enable, allowing the bus to float. The Link device has now asserted its tristate enable, and so drives the PHY-Link bus. If the Link is driving TRANSMIT on its CTL lines, it also drives the first cycle of data on its DATA lines. This turnaround must be completed before the setup time to the PHY, such that the PHY device can know in the next cycle whether the Link device is transmitting or holding.

## Cycle 6

The PHY device 'sees' in this cycle whether the Link drove TRANSMIT or HOLD. If TRANSMIT, it begins to resynchronise the data from the Link device and drive it onto the 1394 bus.

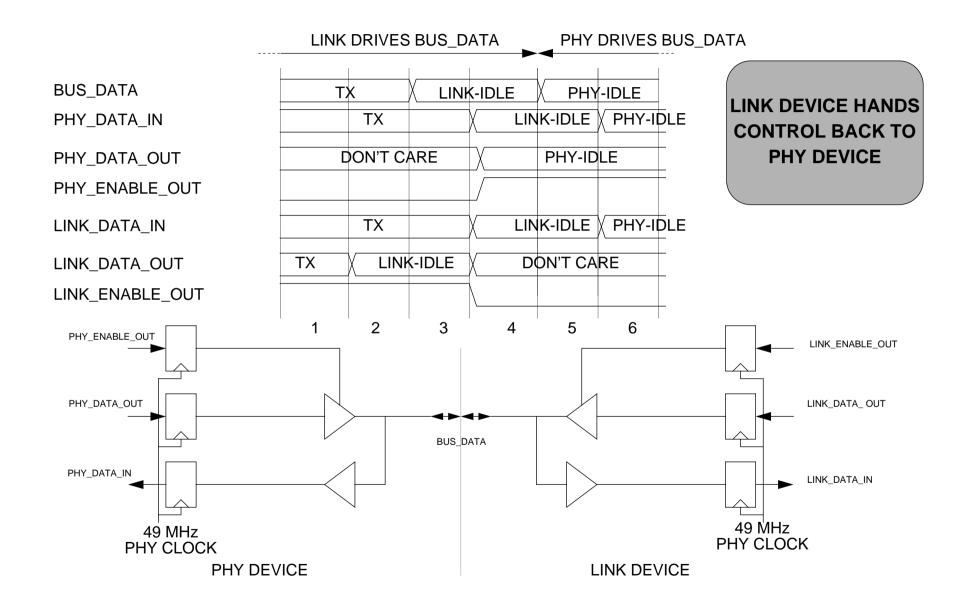

## Description of Interface Behaviour for the Link device handing control back to the PHY device following packet transmission

#### Cycle 1

Link device is transmitting its last cycle of valid data internally on LINK\_DATA\_OUT for the current packet.

#### Cycle 2

Link device transmits its first cycle of IDLE onto its internal LINK\_DATA\_OUT to indicate that it is now complete. The last cycle of valid data from the Link to the PHY is on the PHY-Link bus (BUS\_DATA) during this cycle.

#### Cycle 3

The Link transmits another cycle of IDLE onto its internal LINK\_DATA\_OUT. During this cycle, the first cycle of IDLE driven by the Link device is actually visible on the PHY-Link bus (BUS\_DATA).

#### Cycle 4

The Link device is now complete. It deasserts its own PHY\_ENABLE\_OUT and drives DON'T CARE onto its PHY\_DATA\_OUT.

This is the first cycle that the PHY device actually 'sees' that the Link device is now complete (PHY\_DATA\_IN). Turning around within the same cycle, the PHY device now drives IDLE onto its own PHY\_DATA\_OUT bus, and asserts its tri-state enable signal.

Note that because of the registering of the PHY\_ENABLE\_OUT signals that the Link device is still actually driving BUS\_DATA during this cycle.

#### Cycle 5

The bus turnaround occurs within this cycle. The Link device has de-asserted its tristate enable, allowing the bus to float. The PHY device has now asserted its tristate enable, and so drives the PHY-Link bus.

#### Cycle 6

The Link-PHY bus is now in IDLE for its second cycle.

Note: In the preceding diagram, a distinction is made between PHY-IDLE and LINK-IDLE. In reality, there is no such distinction (both are 00) and the only purpose in indicating a difference is for clarity of the diagram.