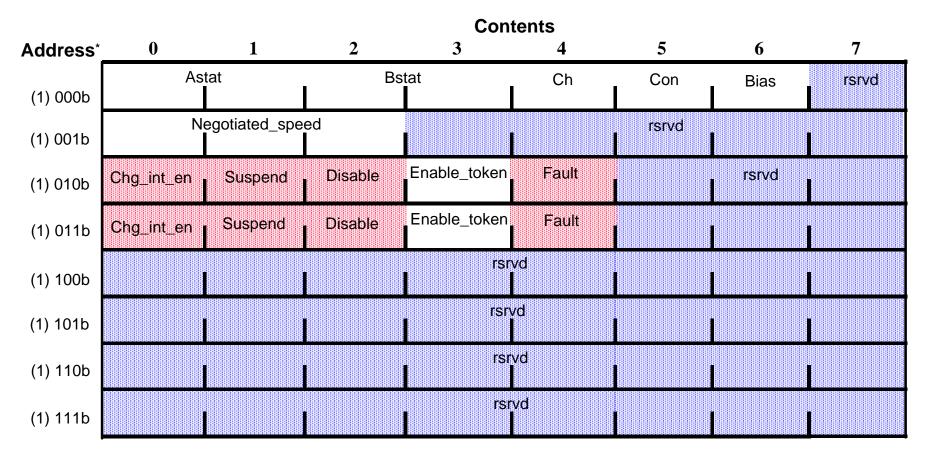

## **PHY Port Register Map**

\*The most significant bit of the address is used only by the link during a PHY register write (Lreq). The most significant bit is **not** used when addressing a port via an extended PHY packet. Register: (1) 010b and (1) 011b - *Control Set* and *Control Clear* (respectively)

| FIELD      | SIZE | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         |

|------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chg_int_en |      |      | <i>change interrupt enable</i> - if set, the PHY will interrupt the link with a Status Packet when one or more of the following bits change state: <i>Con</i> , <i>Bias</i> , <i>Suspend</i> , <i>Fault</i> , or <i>Disable</i> ; this bit is clear subsequent to a power reset;                                                                                    |

| Suspend    |      |      | When writing this bit at register <i>Control Set</i> , the bit does <b>not</b> set, however, the write operation will select the poer as a suspend initiator; writing this bit a register <i>Control Clear</i> will <b>not</b> clear this bit, however the write operation will select the port as a resume initiator; this bit is set subsequent to a power reset. |

| Disable    |      |      | When set, a port is disabled (placing th port in a low power<br>state similar to suspend); a disabled port will not respond to or<br>generate bus resets, suspend notification, or resume events;<br>this bit is clear subsequent to a power reset.                                                                                                                 |

| Enab_token |      |      | Enable token-style arbitration. When set, the enhancements specified in clause 6.5 of the IEEE 1394-1995. A draft specification shall be enabled for this port.                                                                                                                                                                                                     |

| Fault      |      |      | set when a port is not able to successfully interact with its connected port during either a suspend or resume process; this bit is clear subsequent to a power reset.                                                                                                                                                                                              |

| Rsrvd      |      |      | reserved - must not be used or interpreted as having a meaningful value.                                                                                                                                                                                                                                                                                            |

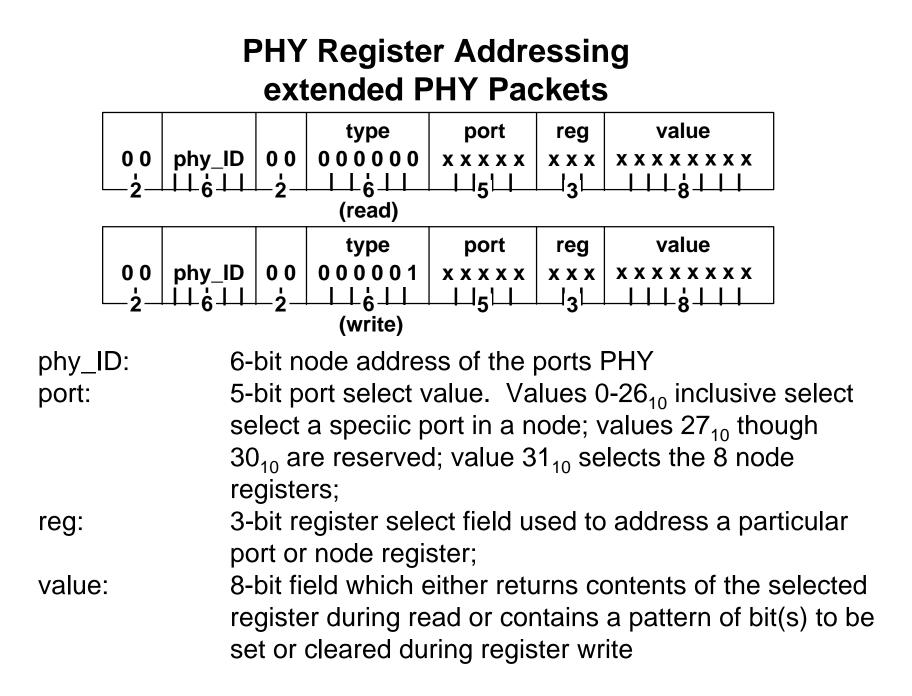

## **PHY Response Packet**

|         |                 |             | type            | port     | reg                | value                                  |

|---------|-----------------|-------------|-----------------|----------|--------------------|----------------------------------------|

| 00      | phy_ID          | 00          | 111111          | X        | ххх                | \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ |

| <b></b> | <b>↓↓↓</b> 6↓↓↓ | <b>-2</b> - | <b>└─┴╘॑┴└─</b> | <u> </u> | <mark>∟ </mark> 3∟ | <b></b>                                |

phy\_ID: 6-bit node ID of node generating the response packet

port: 5-bit port register value (same as the port register

value provided in the extended PHY packet for which the response is being generated);

reg: 3-bit register value (same as the register value provided in the extended PHY packet for which the response is being generated);

value: 8-bit status currently contained in the addressed by the port and reg fields. If an invalid (e.g. reserved) register is addressed, the value will be zero for all bits.

## Extended PHY Packet Type "RESUME"

|                       |          |           | type     | port     | reg            | value       |

|-----------------------|----------|-----------|----------|----------|----------------|-------------|

| 00                    | phy_ID   | 00        | 000010   | 00000    | 011            | 00000010    |

| <b>└</b> _ <b>ż</b> _ | <u> </u> | <b></b> 2 | <u> </u> | <u> </u> | <b>└─</b>  3└─ | └─┼┼┼╞┇┼┼┼┙ |

| phy_ID: | 6-bit node ID of node generating the packet         |

|---------|-----------------------------------------------------|

| type:   | 000010b ( <b>RESUME)</b>                            |

| port:   | 5-bit port register value = 00000b;                 |

| reg:    | 3-bit register value = <i>Control Clear</i> (011b); |

| value:  | 0000010b ( <b>Suspend</b> bit set).                 |

## 1394 Bus Topology Example Revision 0.03 July 14, 1997