# 1. Combined Timing Constants

Table 1 represents the combination of PHY constants from P1394a 1.2 and 1394-1995. The shaded rows indicate which constants are only defined in 1394-1995 and which must be referenced for P1394a PHY design.

**Table 1: Cable PHY timing Constants**

| Timing Constant           | Minimum       | Maximum                    | Comment                                                                                                                                                                                                                                                                |

|---------------------------|---------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |               |                            |                                                                                                                                                                                                                                                                        |

| ACK_RESPONSE_TIME         | 40 ns         | 240 ns                     | Idle time measured at the cable connector from<br>the end of DATA_END that follows a primary<br>packet to the start of DATA_PREFIX that<br>precedes the acknowledge packet.                                                                                            |

| ARB_RESPONSE_DELAY        | 33.3 ns       | PHY_DELAY                  | Delay between an RX_REQUEST signal arriving at the receiving port and the TX_REQUEST signal being sent at the transmit port(s).                                                                                                                                        |

| ARB_SPEED_SIGNAL_START    | -0.02 μs      |                            | Time delay between a transmitting port<br>generating the data_prefix signal and the same<br>transmitting port generating the transmission<br>speed signal                                                                                                              |

| BUS_TO_LINK_DELAY         | PH            | Y_DELAY                    | Data propagation time measured from the Serial Bus connector to the PHY/link interface.                                                                                                                                                                                |

| BASE_RATE                 | 98.294 Mbit/s | 98.314 Mbit/s              | Base bit rate (98.304 $\pm$ 100 ppm) Mbit/s                                                                                                                                                                                                                            |

| CONCATENATION_PREFIX_TIME | 160 ns        |                            | At a transmitting port, the time between the end of clocked data and the start of speed signaling (when present) for the concatenated packet that follows.                                                                                                             |

| CONFIG_TIMEOUT            | 166.6 μs      | 166.9 µs                   | Loop detect time (~16384/BASE_RATE)                                                                                                                                                                                                                                    |

| CONNECT_TIMEOUT           | 336.0 ms      | 341.3 ms                   | Connection debounce time                                                                                                                                                                                                                                               |

| DATA_END_TIME             | 0.24 μs       | 0.26 μs                    | End of packet signal time (~24/BASE_RATE)                                                                                                                                                                                                                              |

| DATA_PREFIX_HOLD          | 40 ns         |                            | At a transmitting port, the time between the end of speed signalling (when present) and the start of clocked data.                                                                                                                                                     |

| DATA_PREFIX_TIME          |               |                            | This timing constant is no longer defined; see DATA_PREFIX_HOLD and MIN_DATA_PREFIX.                                                                                                                                                                                   |

| FORCE_ROOT_TIMEOUT        | 83.3 μs       | CONFIG_TIMEOUT             | Time to wait in state T0 (Tree-ID Start; see 4.4.2.2) before acknowledging Parent_notify signals. (between ~8192/BASE_RATE and ~16384/BASE_RATE)  Important: This time shall be less than or equal to the CONFIG_TIMEOUT value for the node.                           |

| LINK_TO_BUS_DELAY         | 40 ns         | 100 ns                     | Data propagation time measured from the PHY/link interface to the Serial Bus connector.                                                                                                                                                                                |

| MAX_ARB_STATE_TIME        | 200 μs        | 400 μs                     | Maximum time in any state (before a bus reset shall be initiated) except the idle state or a state that exits after an explicit time-out.                                                                                                                              |

| MAX_BUS_HOLD              |               | 1.63 μs                    | Maximum time a node may transmit a TX_DATA_PREFIX signal between the request acknowledge and data packet of concatenated asynchronous subactions or between data packets of concatenated Isochronous subactions. The link shall ensure that this time is not exceeded. |

| MAX_BUS_OCCUPANCY         |               |                            | This timing constant is no longer defined; see MAX_DATA_TIME.                                                                                                                                                                                                          |

| MAX_DATA_TIME             |               | 84.31 μs                   | The maximum time that clocked data may be transmitted continuously. If this limit is exceeded, unpredictable behavior may result.                                                                                                                                      |

| MAX_DATA_PREFIX_DELAY     |               | PHY_DELAY (see table 4-29) | Maximum delay between a RX_DATA_PREFIX signal arriving at a receive port and a TX_DATA_PREFIX being sent at a transmit                                                                                                                                                 |

|                        |            |            | port                                                                                  |

|------------------------|------------|------------|---------------------------------------------------------------------------------------|

|                        |            |            | (this means that the data prefix signal has to be delayed less than the clocked data) |

| MIN_DATA_PREFIX        | 140 ns     |            | The total time an originating port transmits a                                        |

|                        |            |            | TX_DATA_PREFIX signal prior to clocked                                                |

|                        |            |            | data.                                                                                 |

| MIN_PACKET_SEPARATION  | 0.34 μs    |            | Minimum time between packets (~32/BASE_RATE)                                          |

| NOMINAL_CYCLE_TIME     | 124.988 µs | 125.013 μs | Average time between the start of one                                                 |

|                        |            |            | isochronous cycle and the next (125 $\mu$ s $\pm$ 100                                 |

|                        |            |            | ppm)                                                                                  |

| PHY_DELAY              | 80 ns      | See PHY    | Best-case repeater data delay has a fixed                                             |

| DING DEGRONGE WINE     | 50         | registers  | minimum.                                                                              |

| PING_RESPONSE_TIME     | 50 ns      | 240 ns     | Time permitted a PHY to respond to a ping packet (see clause 7.4.5), measured at the  |

|                        |            |            | connector from the end of DATA_END to the                                             |

|                        |            |            | start of DATA_PREFIX for the first self-ID                                            |

|                        |            |            | packet.                                                                               |

| RESET_DETECT           | 80.0 ms    | 85.3 ms    | Time for a connected node to confirm a reset                                          |

|                        |            |            | signal                                                                                |

| RESET_TIME             | 166.6 µs   | 166.7 μs   | Reset hold time (~16384/BASE_RATE)                                                    |

| RESET_WAIT             | 0.16 μs    |            | Reset wait delta time. (~16/BASE_RATE)                                                |

| ROOT_CONTEND_FAST      | 0.76 μs    | 0.80 µs    | Time to wait in state T3: Root Contention if the                                      |

|                        |            |            | random bit is zero, as described in clause 4.4.2.2                                    |

|                        |            |            | of IEEE Std 1394-1995. (~80/BASE_RATE)                                                |

| ROOT_CONTEND_SLOW      | 1.60 µs    | 1.64 µs    | Time to wait in state T3: Root Contention if the                                      |

|                        |            |            | random bit is one, as described in clause 4.4.2.2                                     |

| GUODE DEGEE ETVE       | 1.20       | 1.40       | of IEEE Std 1394-1995. (~160/BASE_RATE)                                               |

| SHORT_RESET_TIME       | 1.30 μs    | 1.40 μs    | Short reset hold time. (~128/BASE_RATE)                                               |

| SID_SPEED_SIGNAL_START | -0.02 μs   | 0.02μs     | Time delay between a child port generating the                                        |

|                        |            |            | TX_IDENT_DONE signal and the same child port generating the speed capability signal   |

| SPEED_SIGNAL_LENGTH    | 0.10 μs    | 0.12 μs    | Time while speed signaling is active                                                  |

| SEED_SIGNAL_TENGIH     | 0.10 μs    | 0.12 μs    | (~10/BASE_RATE)                                                                       |

|                        |            |            | (*10/DADE_KATE)                                                                       |

### 2. Suggested Changes

Based on our consensus review at the PHYDOG's meeting in Albuquerque, the following modifications are proposed for P1394a to clarify intent, correct errors, etc.

#### **Table Title**

Some of the parameters in the table are not guaranteed by the PHY, but are required to characterize a node's behavior at the 1394 interface. One example is NOMINAL\_CYCLE\_TIME. Proposal is to change the table title to "Cable interface timing constants" since the constants are node specific rather than PHY specific.

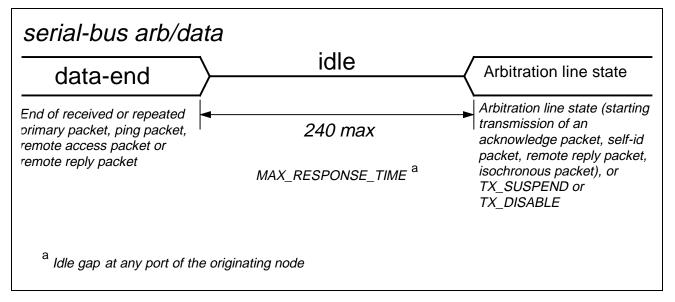

#### ACK RESPONSE TIME → MAX RESPONSE TIME

Per the Albuquerque PHY designer's review session, this parameter is intended to subsume the PING\_RESPONSE\_TIME and specifies the time by which a node must commence any response required to be received before a subaction\_gap is detected anywhere within the network. Responses which must be received within the same subaction include acknowledge packets, isochronous packets, remote reply packets, self-id packets, and TX\_SUSPEND/TX\_DISABLE indications. Consequently, the comment should be updated to:

Idle time measured at the cable connector from the end of DATA\_END that follows a primary packet, ping packet, remote access packet or remote reply packet to the start of the DATA\_PREFIX for an ACK packet, a self\_ID packet, a remote reply packet, an isochronous packet, or a TX\_SUSPEND or TX\_DISABLE. See **Error! Reference source not found.**

## ARB RESPONSE DELAY

This timing parameter was intended to bound the PHY's response to any received arbitration indication. It defines the time for repeating a TX\_REQUEST signal, the delay of DATA\_PREFIX through the node, etc. It subsumes the MAX\_DATA\_PREFIX\_DELAY parameter as well. The comment needs to be updated:

Arbitration delay of a node measured between the start of reception of an arbitration signal at the receiving port and the start of transmission of a corresponding arbitration indication at any port (including the initial receive port).

Note: The maximum specification of PHY\_DELAY guarantees that arbitration indications are repeated no slower than clocked data.

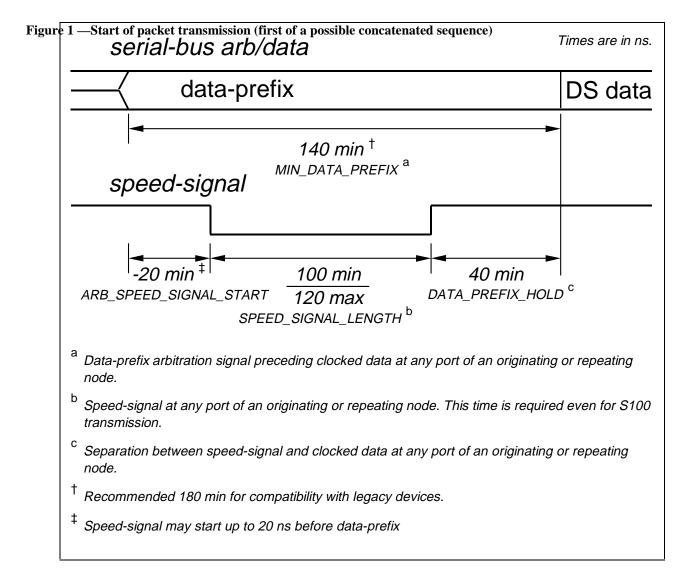

## ARB SPEED SIGNAL START

This parameter only applies to the first packet after IDLE or RX\_GRANT. Said differently, this parameter does not specify the relationship of the speed signaling to the DATA\_PREFIX of concatenated packets. As such, the comment should be clarified and a reference to the figure added:

Time delay between a transmitting port generating the DATA\_PREFIX signal and the same transmitting port generating the transmission speed signal for the first packet in a possible concatenated sequence. See Figure 1.

## **BUS TO LINK DELAY**

This parameter is not required to specify node behavior when viewed from the 1394 interface. In fact, compliance to this parameter can not be determined from the 1394 connector. This parameter was added to aid the "pinging" calculations and the only contribution to the pinging calculation comes from the BUS\_TO\_LINK\_DELAY of the device initiating the ping. In general, the node performing the pinging can know the bus-to-link delay of it's own PHY/LINK combination through non-normative means. Consequently, BUS\_TO\_LINK should not be part of the normative Clause 7 interface parameters. However, there is a need for nodes that employ discrete PHY's to know the BUS\_TO\_LINK delay contribution from its attached PHY. As such, BUS\_TO\_LINK\_DELAY should be moved to the timing parameters for Clause 5 and the comment modified to read:

Delay from receiving DATA\_PREFIX on a receive port to transmitting Receive on CTL[0:1] at the PHY/Link interface.

As part of the clause 5 specification, it is also more appropriate to specify timings in terms of SCLK cycles and the MIN/MAX values are recalculated as such.

This change will affect OHCI generic software that may assume BUS\_TO\_LINK\_DELAY applies regardless of whether the PHY is integrated or discrete. The proper fix for this is to add the necessary constants into OHCI, not to constrain integrated PHY designs in P1394a.

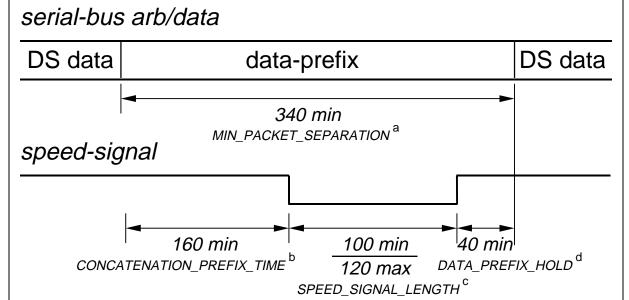

### **CONCATENATION PREFIX TIME**

When transmitting concatenated packets, originating and repeating PHY's shall ensure that CONCATENATION\_PREFIX\_TIME + SPEED\_SIGNAL\_LENGTH + DATA\_PREFIX\_HOLD is met even when no speed-signaling is present. The comment for CONCATENATION\_PREFIX\_TIME should be adjusted to suggest that the speed signaling time is always required and to reference the appropriate figure:

At a transmitting port, the time between the end of clocked data and the start of the speed signaling time for the concatenated packet that follows. See Figure 2.

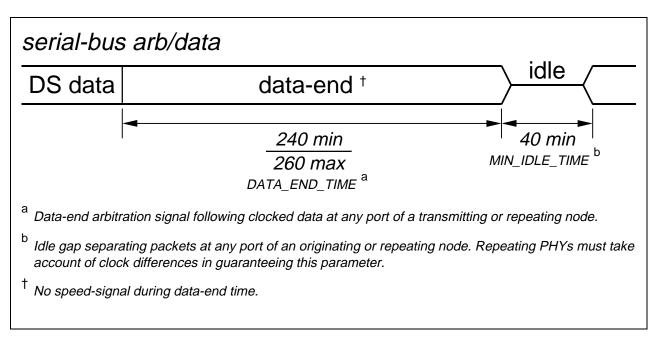

## DATA\_END\_TIME

A figure illustrating the end of packet transmission has been prepared and should be referenced in the comment:

End of packet signal time (~24/BASE\_RATE). See Figure 3.

## DATA\_PREFIX\_HOLD

When transmitting concatenated packets, originating and repeating PHY's shall ensure that CONCATENATION\_PREFIX\_TIME + SPEED\_SIGNAL\_LENGTH + DATA\_PREFIX\_HOLD is met even when no speed-signaling is present. The comment for DATA\_PREFIX\_HOLD should be adjusted to suggest that the speed signaling time is always required and to reference the appropriate figures:

At a transmitting port, the time between the end of the speed signaling time and the start of clocked data. See Figure 1 and Figure 2.

#### LINK TO BUS DELAY

This parameter is not required to specify node behavior when viewed from the 1394 interface. In fact, compliance to this parameter can not be determined from the 1394 connector. This parameter was added to aid the "pinging" calculations and the only contribution to the pinging calculation comes from the LINK\_TO\_BUS\_DELAY of the device initiating the ping. In general, the node performing the pinging can know the link-to-bus delay of it's own PHY/LINK combination through non-normative means. Consequently, LINK\_TO\_BUS should not be part of the normative Clause 7 interface parameters. However, there is a need for nodes that employ discrete PHY's to know the LINK\_TO\_BUS delay contribution from its attached PHY. As such, LINK\_TO\_BUS\_DELAY should be moved to the timing parameters for Clause 5 and the comment modified to read:

Delay from first Idle on CTL[0:1] in which the link releases the PHY/Link interface to the start of DATA\_END following the originated packet on all transmit ports.

As part of the clause 5 specification, it is also more appropriate to specify timings in terms of SCLK cycles and the MIN/MAX values are recalculated as such.

This change will affect OHCI generic software that may assume LINK\_TO\_BUS\_DELAY applies regardless of whether the PHY is integrated or discrete. The proper fix for this is to add the necessary constants into OHCI, not to constrain integrated PHY designs in P1394a.

## MAX\_BUS\_HOLD

With fly-by acceleration, asynchronous concatenations can occur on the ack following both request and response primary packets. Consequently, MAX\_BUS\_HOLD should be extended to the total amount of DATA\_PREFIX between the acknowledge of any primary asynch packet and the following concatenated primary packet. Furthermore, only the node originating the concatenation can be responsible for enforcing MAX\_BUS\_HOLD. As such, the MAX\_BUS\_HOLD comment should be modified to read:

Maximum time an originating node may transmit a TX\_DATA\_PREFIX signal between the acknowledge and data packet of concatenated asynchronous subactions or between data packets of concatenated isochronous subactions. The link shall ensure that this time is not exceeded.

When a discrete PHY is employed, the attached link is responsible for ensuring MAX\_BUS\_HOLD is met. However, the current P1394a draft doesn't provide sufficient information for the link to guarantee it doesn't exceed MAS\_BUS\_HOLD. For example, the link doesn't know how long the PHY asserts DATA\_PREFIX on the wire before granting the link. To ensure a discrete PHY and link cooperate to properly meet MAX\_BUS\_HOLD, two new parameters are defined for inclusion in Clause 5. (The parameters are not externally visible and only pertain to the PHY/Link interface.)

MAX\_DATA\_PREFIX\_TO\_GRANT bounds the duration of the DATA\_PREFIX the PHY asserts on the 1394 bus before granting the link to transmit. The precise definition is given as:

Delay from PHY first sending DATA\_PREFIX at a port to asserting Grant on CTL[0:1] at the PHY/Link interface.

MAX\_HOLD\_CYCLES limits the number of HOLD indications the link can use to delay transmission of a packet once the interface has been granted by the PHY. The precise definition is given as:

Maximum duration of consecutive HOLD indications the link can drive on CTL[0:1] after sampling Grant and before asserting Transmit.

Since the PHY/Link interface can take as many as three cycles to turn around (GRANT-IDLE-IDLE), the DATA\_PREFIX time on the 1394 bus between concatenations can be given (in cycles) as MAX\_DATA\_PREFIX\_TO\_GRANT + 3 + MAX\_HOLD\_CYCLES + LINK\_TO\_BUS\_DELAY. With the proposed parameters, the maximum DATA\_PREFIX time caused by the link during concatenation will be 80 cycles or 1627 ns, just shy of the 1630 ns MAX\_BUS\_HOLD requirement.

## MAX\_DATA\_PREFIX\_DELAY

This parameter is superceded by ARB\_RESPONSE\_DELAY which, for the purpose of gap count analysis, bounds the minimum and maximum time the PHY uses to repeat or respond to any received arbitration indication (not just DATA\_PREFIX). Comment becomes:

This timing constant is no longer defined; see ARB\_RESPONSE\_DELAY.

## MIN\_DATA\_PREFIX

This parameter only applies to the first packet after IDLE or RX\_GRANT. Said differently, this parameter does not specify the duration of DATA\_PREFIX in between concatenated packets. As such, the comment should be clarified and a reference to the figure added:

The total time an originating port transmits a TX\_DATA\_PREFIX signal prior to clocked data for the first packet in a possible concatenated sequence. See Figure 1.

#### MIN IDLE TIME

All nodes must enforce a minimum idle gap after the DATA\_END of a packet sequence. This minimum time used to be accounted for by the minimum ACK\_RESPONSE\_TIME. However, ACK\_RESPONSE\_TIME and the new MAX\_RESPONSE\_TIME only apply at the originating node. Consequently, a new parameter that applied at every transmitting port was required. The definition of MIN\_IDLE\_TIME is:

Idle gap separating packets at any port of an originating or repeating node. See Figure 3.

## MIN\_PACKET\_SEPARATION

This parameter only applies to the duration of DATA\_PREFIX between concatenated packets and is only enforced at the node that originates the concatenation. Also, the originally specified guideline of  $\sim 32/BASE\_RATE$  is in error. The .34  $\mu$ S minimum is actually closer to  $\sim 34/BASE\_RATE$ . The comment should also include a reference to the new figure:

The total duration of the TX\_DATA\_PREFIX signal separating clocked data of concatenated packets at any port of an originating node. See Figure 2. (~34/BASE\_RATE)

## PING RESPONSE TIME

This parameter is superceded by the MAX\_RESPONSE\_TIME constant which defines the max Idle time that can be sustained at any originating port while still ensuring a subaction\_gap isn't detected in the network. Such a parameter is needed for more than just acks and pings. Comment becomes:

This timing constant is no longer defined; see MAX\_RESPONSE\_TIME.

## SPEED\_SIGNAL\_LENGTH

The speed signaling period must be guaranteed by any transmitting port. This is true even in the case of S100 when no speed code is actually signaled. The comment should clarify this requirement and reference the new diagrams:

Duration of speed signaling at a transmitting port. See Figure 1 and Figure 2. ( $\sim 10/BASE\_RATE$ )

**Important:** This time period is required for S100 packet transmission even though an explicit speed signal is not sent.

# 3. Updated Tables

Table 2 provides a single table of all Clause 7 constants complete with all of the proposed modifications. The intent is to have Table 2 complete replace Table 4-32 from the IEEE1394-1995 specification. This will allow designers to clearly see all of the necessary constants in a single consistent location.

Table 3 contains the interface constants which should be moved into Clause 5 since the pertain only to the PHY/Link interface.

**Table 2: Cable interface timing Constants**

| Timing Constant           | Minimum       | Maximum        | Comment                                                                                                                                                                                                                                                                     |

|---------------------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARB_RESPONSE_DELAY        | 33.3 ns       | PHY_DELAY      | Arbitration delay of a node measured between the start of reception of an arbitration signal at the receiving port and the start of transmission of a corresponding arbitration indication at any port (including the initial receive port).                                |

|                           |               |                | Note: The maximum specification of PHY_DELAY guarantees that arbitration indications are repeated no slower than clocked data.                                                                                                                                              |

| ARB_SPEED_SIGNAL_START    | -0.02 μs      |                | Time delay between a transmitting port generating the DATA_PREFIX signal and the same transmitting port generating the transmission speed signal for the first packet in a possible concatenated sequence. See Figure 1.                                                    |

| BASE_RATE                 | 98.294 Mbit/s | 98.314 Mbit/s  | Base bit rate (98.304 ± 100 ppm) Mbit/s                                                                                                                                                                                                                                     |

| CONCATENATION_PREFIX_TIME | 160 ns        |                | At a transmitting port, the time between the end of clocked data and the start of the speed signaling time for the concatenated packet that follows. See Figure 2.                                                                                                          |

| CONFIG_TIMEOUT            | 166.6 μs      | 166.9 μs       | Loop detect time (~16384/BASE_RATE)                                                                                                                                                                                                                                         |

| CONNECT_TIMEOUT           | 336.0 ms      | 341.3 ms       | Connection debounce time                                                                                                                                                                                                                                                    |

| DATA_END_TIME             | 0.24 μs       | 0.26 μs        | End of packet signal time (~24/BASE_RATE). See Figure 3.                                                                                                                                                                                                                    |

| DATA_PREFIX_HOLD          | 40 ns         |                | At a transmitting port, the time between the end of the speed signaling time and the start of clocked data. See Figure 1 and Figure 2.                                                                                                                                      |

| DATA_PREFIX_TIME          |               |                | This timing constant is no longer defined; see DATA_PREFIX_HOLD and MIN_DATA_PREFIX.                                                                                                                                                                                        |

| FORCE_ROOT_TIMEOUT        | 83.3 μs       | CONFIG_TIMEOUT | Time to wait in state T0 (Tree-ID Start; see 4.4.2.2) before acknowledging Parent_notify signals. (between ~8192/BASE_RATE and ~16384/BASE_RATE) Important: This time shall be less than or equal to the CONFIG_TIMEOUT value for the node.                                 |

| MAX_ARB_STATE_TIME        | 200 μs        | 400 μs         | Maximum time in any state (before a bus reset shall be initiated) except the idle state or a state that exits after an explicit time-out.                                                                                                                                   |

| MAX_BUS_HOLD              |               | 1.63 μs        | Maximum time an originating node may transmit a TX_DATA_PREFIX signal between the acknowledge and data packet of concatenated asynchronous subactions or between data packets of concatenated isochronous subactions. The link shall ensure that this time is not exceeded. |

| MAX_BUS_OCCUPANCY         |               |                | This timing constant is no longer defined; see MAX_DATA_TIME.                                                                                                                                                                                                               |

| MAX_DATA_TIME             |               | 84.31 µs       | The maximum time that clocked data may be                                                                                                                                                                                                                                   |

|                        |            |            | transmitted continuously. If this limit is                                              |

|------------------------|------------|------------|-----------------------------------------------------------------------------------------|

|                        |            |            | transmitted continuously. If this limit is exceeded, unpredictable behavior may result. |

| MAX DATA PREFIX DELAY  |            |            | This timing constant is no longer defined; see                                          |

| MAX_DATA_FREFTX_DEDAT  |            |            | ARB_RESPONSE_DELAY.                                                                     |

| MAY DECDONCE TIME      |            | 240 ns     | Idle time measured at the cable connector from                                          |

| MAX_RESPONSE_TIME      |            | 240 ns     | the end of DATA_END that follows a primary                                              |

|                        |            |            |                                                                                         |

|                        |            |            | packet, ping packet, remote access packet or remote reply packet to the start of the    |

|                        |            |            | DATA_PREFIX for an ACK packet, a self_ID                                                |

|                        |            |            | packet, a remote reply packet, an isochronous                                           |

|                        |            |            | packet, a remote reply packet, an isochronous packet, or a TX_SUSPEND or TX_DISABLE.    |

|                        |            |            | See Figure 4.                                                                           |

| MIN_DATA_PREFIX        | 140 ns     |            | The total time an originating port transmits a                                          |

| MIN_DATA_FREFIX        | 140 113    |            | TX_DATA_PREFIX signal prior to clocked data                                             |

|                        |            |            | for the first packet in a possible concatenated                                         |

|                        |            |            | sequence. See Figure 1.                                                                 |

| MIN_IDLE_TIME          | 40 ns      |            | Idle gap separating packets at any port of an                                           |

|                        | 70 115     |            | originating or repeating node. See Figure 3.                                            |

| MIN_PACKET_SEPARATION  | 0.34 μs    |            | The total duration of the TX_DATA_PREFIX                                                |

|                        | 0.5 Γμ5    |            | signal separating clocked data of concatenated                                          |

|                        |            |            | packets at any port of an originating node. See                                         |

|                        |            |            | Figure 2.                                                                               |

|                        |            |            | (~34/BASE_RATE)                                                                         |

| NOMINAL_CYCLE_TIME     | 124.988 μs | 125.013 μs | Average time between the start of one                                                   |

|                        | •          | •          | isochronous cycle and the next (125 $\mu$ s $\pm$ 100                                   |

|                        |            |            | ppm)                                                                                    |

| PHY_DELAY              | 80 ns      | See PHY    | Best-case repeater data delay has a fixed                                               |

|                        |            | Registers  | minimum.                                                                                |

| PING_RESPONSE_TIME     | 50 ns      | 240 ns     | This timing constant is no longer defined; see                                          |

|                        |            |            | MAX_RESPONSE_TIME.                                                                      |

| RESET_DETECT           | 80.0 ms    | 85.3 ms    | Time for a connected node to confirm a reset                                            |

|                        |            |            | signal                                                                                  |

| RESET_TIME             | 166.6 μs   | 166.7 μs   | Reset hold time (~16384/BASE_RATE)                                                      |

| RESET_WAIT             | 0          | .16 μs     | Reset wait delta time. (~16/BASE_RATE)                                                  |

| ROOT_CONTEND_FAST      | 0.76 μs    | 0.80 μs    | Time to wait in state T3: Root Contention if the                                        |

|                        |            | ·          | random bit is zero, as described in clause 4.4.2.2                                      |

|                        |            |            | of IEEE Std 1394-1995. (~80/BASE_RATE)                                                  |

| ROOT_CONTEND_SLOW      | 1.60 µs    | 1.64 µs    | Time to wait in state T3: Root Contention if the                                        |

|                        |            |            | random bit is one, as described in clause 4.4.2.2                                       |

|                        |            |            | of IEEE Std 1394-1995. (~160/BASE_RATE)                                                 |

| SHORT_RESET_TIME       | 1.30 μs    | 1.40 µs    | Short reset hold time. (~128/BASE_RATE)                                                 |

| SID_SPEED_SIGNAL_START | -0.02 μs   | 0.02μs     | Time delay between a child port generating the                                          |

|                        |            | •          | TX_IDENT_DONE signal and the same child                                                 |

|                        |            |            | port generating the speed capability signal                                             |

| SPEED_SIGNAL_LENGTH    | 0.10 μs    | 0.12 μs    | Duration of speed signaling at a transmitting                                           |

|                        |            |            | port. See Figure 1 and Figure 2.                                                        |

|                        |            |            | (~10/BASE_RATE)                                                                         |

|                        |            |            |                                                                                         |

|                        |            |            | <b>Important:</b> This time period is required for                                      |

|                        |            |            | S100 packet transmission even though an                                                 |

|                        |            |            | explicit speed signal is not sent.                                                      |

**Table 3: PHY/Link interface timing Constants**

| Timing Constant   | Minimum  | Maximum  | Comment                                           |

|-------------------|----------|----------|---------------------------------------------------|

| BUS_TO_LINK_DELAY | 2 cycles | 9 cycles | Delay from receiving DATA_PREFIX on a             |

|                   |          |          | receive port to transmitting Receive on CTL[0:1]  |

|                   |          |          | at the PHY/Link interface.                        |

| LINK_TO_BUS_DELAY | 2 cycles | 5 cycles | Delay from first Idle on CTL[0:1] in which the    |

|                   | ·        |          | link releases the PHY/Link interface to the start |

|                          |           | of DATA_END following the originated packet on all transmit ports.                                                                  |

|--------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| MAX_DATA_PREFIX_TO_GRANT | 25 cycles | Delay from PHY first sending DATA_PREFIX at a port to asserting Grant on CTL[0:1] at the PHY/Link interface.                        |

| MAX_HOLD_CYCLES          | 47 cycles | Maximum duration of consecutive HOLD indications the link can drive on CTL[0:1] after sampling Grant and before asserting Transmit. |

## 4. Proposed Figures

The following figures were reviewed and adopted at the Albuquerque PHYDOG's meeting.

Figure 2 — Concatenated packet transmission

Data-prefix arbitration signal separating clocked data of concatenated packets at any port of an originating node. A repeating node may generate less due to clock frequency and phase differences.

Separation between clocked data and the speed-signal for a concatenated packet at any port of an originating or repeating node.

<sup>&</sup>lt;sup>C</sup> Speed-signal at any port of an originating or repeating node. This time is required even for S100 transmission.

d Separation between speed-signal and clocked data at any port of an originating or repeating node.

Figure 3 —End of packet transmission

Figure 4 —Response Time to prevent detection of a subaction\_gap