# P1394a Draft Standard for a High Performance Serial Bus (Supplement)

Sponsor

Microprocessor and Microcomputer Standards Committee of the IEEE Computer Society

Not yet Approved by

**IEEE Standards Board**

Not yet Approved by American National Standards Institute

**Abstract:** Supplemental information for a high-speed serial bus that integrates well with most IEEE standard 32-bit and 64-bit parallel buses is specified. It is intended to extend the usefulness of a low-cost interconnect between external peripherals. This standard follows the IEEE Std 1212-1991 Command and Status Register (CSR) architecture.

Keywords: bus, computers, high-speed serial bus, interconnect

ISBN x-xxxxx-xxx-x

The Institute of Electrical And Electronics Engineers, Inc. 345 East 47th Street, New York, NY 10017-2394, USA

Copyright © 1997 by the Institute of Electrical And Electronics Engineers, Inc. All rights reserved. Published 1997. Printed in the United States of America.

This is an unapproved IEEE Standards Draft, subject to change. Permission is hereby granted for IEEE Standards Committee participants to reproduce this document for purposes of IEEE standardization activities, including balloting and coordination. If this document is to be submitted to ISO or IEC, notification shall be given to the IEEE Copyright Administrator. Permission is also granted for member bodies and technical committees of ISO and IEC to reproduce this document for purposes of developing a national position. Other entities seeking permission to reproduce this document for these or other uses must contact the IEEE Standards Department for the appropriate license. Use of the information contained in this unapproved draft is at your own risk.

**IEEE Standards** documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; (508) 750-8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

# Introduction

(This introduction is not a part of IEEE Std 1394-1995, IEEE Standard for a High Performance Serial Bus (Supplement).)

This standards effort started in 1996 at the request of...

### **Patent notice**

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

The patent holder has, however, filed a statement of assurance that it will grant a license under these rights without compensation or under reasonable rates and nondiscriminatory, reasonable terms and conditions to all applicants desiring to obtain such a license. The IEEE makes no representation as to the reasonableness of rates and/or terms and conditions of the license agreement offered by the patent holder. Contact information may be obtained from the IEEE Standards Department.

### **Committee membership**

The following is a list of voting members of the IEEE P1394a working group at the time of publication.

Peter Johansson, Chair and Editor Dick Scheel, Secretary

The following is a list of other major participants in the IEEE P1394a working group (those that attended at least three working group meetings in the last four years).

| Dave Banks        | Taka Fujimori      | Jim Koser        | Bob Plummer         |

|-------------------|--------------------|------------------|---------------------|

| Max Bassler       | John Fuller        | Takashi Kubo     | Matt Pujol          |

| Harrison Beasley  | Masamichi Furukawa | Steve Kukla      | Mehran Ramezani     |

| Erich Berndlmaier | Mike Gardner       | Tadashi Kumihira | Dennis Rehm         |

| David Brief       | Ram Gopalan        | Farrukh Latif    | Todd Roper          |

| Mike Brown        | Gordon Haas        | Aaron Ludtke     | Bill Russell        |

| Joe Chen          | Manish Harpalani   | Jerry Marazas    | Takashi Sato        |

| Rajiv Choudhary   | Katsuya Hasegawa   | Tetsuya Miyame   | Dick Scheel         |

| Richard Churchill | Yasumasa Hasegawa  | Kazayoshi Moriya | Andreas Schloissnik |

| Alistair Coles    | Shinichi Hatae     | Shuhei Moriyoshi | Imran Sharif        |

| Hugh Curley       | Jerry Hauck        | Richard Mourn    | Robbie Shergill     |

| Bill Duckwall     | Burke Henehan      | Bill Northey     | Hisato Shima        |

| Brian G. Dugan    | Jack Hollins       | Karen O'Connell  | Michael Sorna       |

| Mike Eneboe       | Du Hung Hou        | Yasushi Ohtani   | Curtis Stevens      |

| Dave Evans        | David James        | Jun Okazaki      | Tom Suters          |

| Lou Fasano        | Peter Johansson    | Erik Ottem       | Shah Talukder       |

| Steve Finch       | Tony Kobayashi     | Alan Perry       | Mike Teener         |

|                   |                    |                  |                     |

The following persons served on the ballot response committee:

The following persons were members of the balloting group:

If the IEEE Standards Board approves this draft standard, it might have the following membership:

#### E. G. "Al" Kiener, Chair

#### Andrew G. Salem, Secretary

Gilles A. Baril Clyde R. Camp Joseph A. Cannatelli Stephen L. Diamond Harold E. Epstein Donald C. Fleckenstein Jay Forster\* Donald N. Heirman Richard J. Holleman

\*Member Emeritus

Jim Isaak Ben C. Johnson Sonny Kasturi Lorraine C. Kevra Ivor N. Knight Joseph L. Koepfinger\* D. N. "Jim" Logothetis L. Bruce McClung Marco W. Migliaro Mary Lou Padgett John W. Pope Arthur K. Reilly Gary S. Robinson Ingo Rüsch Chee Kiow Tan Leonard L. Tripp Howard L. Wolfman

Donald C. Loughry, Vice Chair

Other candiates for inclusion might be the following nonvoting IEEE Standards Board liaisons:

Satish K. Aggarwal Steve Sharkey Robert E. Hebner Chester C. Taylor

Mary Lynne Nielsen IEEE Standards Project Editor

| 1. Overview                                                    | 1  |

|----------------------------------------------------------------|----|

| 1.1 Scope                                                      |    |

| 1.2 Purpose                                                    | 1  |

| 1.3 References                                                 |    |

| 1.4 Document organization                                      |    |

| 1.5 Service model                                              |    |

| 1.6 Document notation                                          |    |

| 2. Definitions and abbreviations                               |    |

| 2.1 Conformance glossary                                       |    |

| 2.2 Technical glossary                                         |    |

| 3. Summary description                                         | 17 |

| 4. Alternative cable media attachment specification            |    |

| 4.1 Connectors                                                 |    |

| 4.2 Cables                                                     |    |

| 4.3 Connector and cable assembly performance criteria          |    |

| 4.4 Signal propagation performance criteria                    |    |

| 5. PHY/Link interface specification                            |    |

| 5.1 Operation                                                  |    |

| 5.2 PHY register map                                           |    |

| 5.3 AC timing                                                  |    |

| 6. Cable physical layer performance enhancement specifications |    |

| 6.1 Cable PHY packets                                          |    |

| 6.2 Cable PHY timing constants                                 |    |

| 6.3 Cable physical layer operation                             |    |

| 6.4 Tree identify resolution of looped topologies              |    |

| 6.5 Port disable                                               |    |

| 7. Isochronous connection management specifications            |    |

| 7.1 Plug control registers                                     |    |

| 7.2 Isochronous connection management                          |    |

| 8. Request and response error handling specifications          | 97 |

| 9. Clarifications and corrigenda                               |    |

| 9.1 Automatic enablement of the cycle master                   |    |

| 9.2 Unit registers                                             |    |

| 9.3 Transaction layer services                                 |    |

| 9.4 Response codes                                             |    |

| Figure 1-1— Service model                                                          | 3  |

|------------------------------------------------------------------------------------|----|

| Figure 1-2— Bit and byte ordering                                                  | 4  |

| Figure 1-3— Example packet format                                                  | 5  |

| Figure 1-4— State machine example                                                  | 6  |

| Figure 1-5— CSR format specification (example)                                     | 7  |

| Figure 1-6— Reserved fields                                                        | 9  |

| Figure 4-1 — Plug body                                                             | 20 |

| Figure 4-2 — Plug section details                                                  |    |

| Figure 4-3 — Connector socket interface                                            | 22 |

| Figure 4-5 — Cross-section of plug and socket contacts                             | 23 |

| Figure 4-4 — Socket cross-section A–A                                              | 23 |

| Figure 4-6 — Socket position when mounted on a PCB                                 | 24 |

| Figure 4-7 — Flat surface mount PCB connector footprint                            | 25 |

| Figure 4-8 — Flat through-hole mount PCB connector footprint                       |    |

| Figure 4-9 — Cable material construction example (for reference only)              |    |

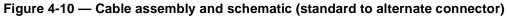

| Figure 4-10 — Cable assembly and schematic (standard to alternate connector)       |    |

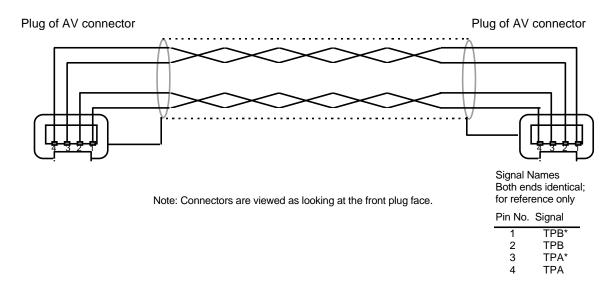

| Figure 4-11— Cable assembly and schematic (alternate connectors)                   |    |

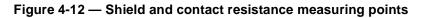

| Figure 4-12 — Shield and contact resistance measuring points                       |    |

| Figure 4-13 — Fixture for cable flex test                                          |    |

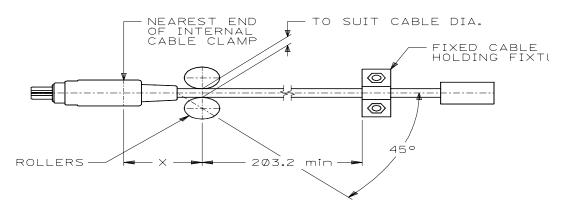

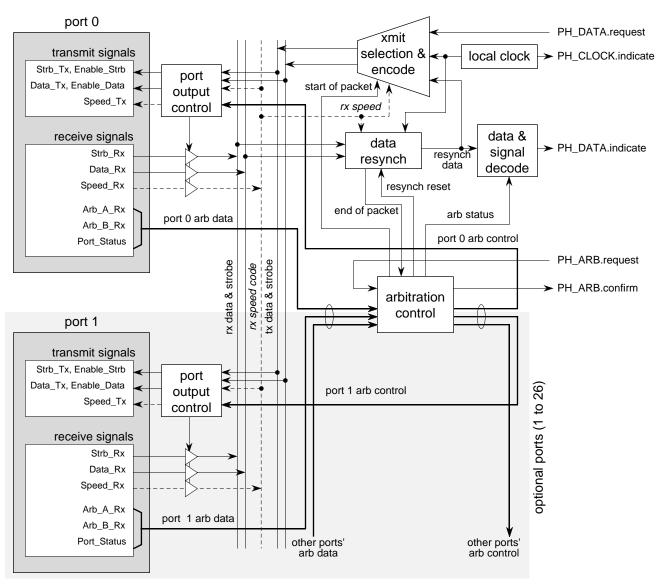

| Figure 5-1 — PHY-Link interface                                                    |    |

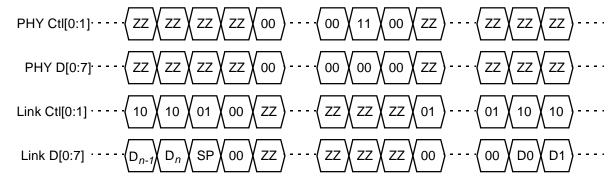

| Figure 5-2 — LReq timing                                                           |    |

| Figure 5-3 — Status timing                                                         |    |

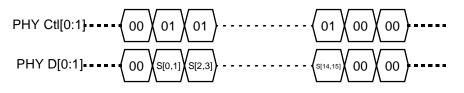

| Figure 5-4 — Transmit timing                                                       |    |

| Figure 5-5 — Receive timing                                                        |    |

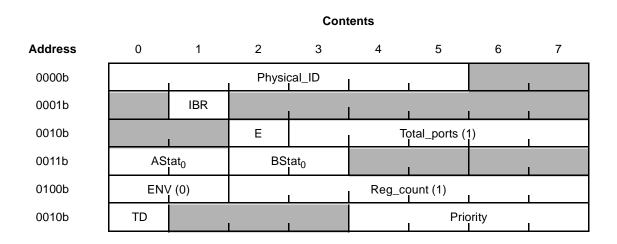

| Figure 5-6 — Legacy PHY register map for the cable environment                     |    |

| Figure 5-7 — Extended PHY register map for the cable environment                   |    |

| Figure 5-8 — PHY register page 0: Port Status page                                 |    |

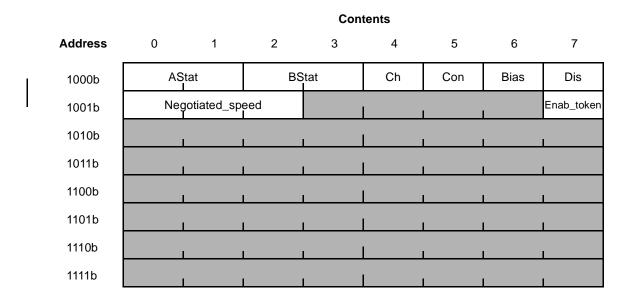

| Figure 5-9 — PHY register map for the backplane environment                        |    |

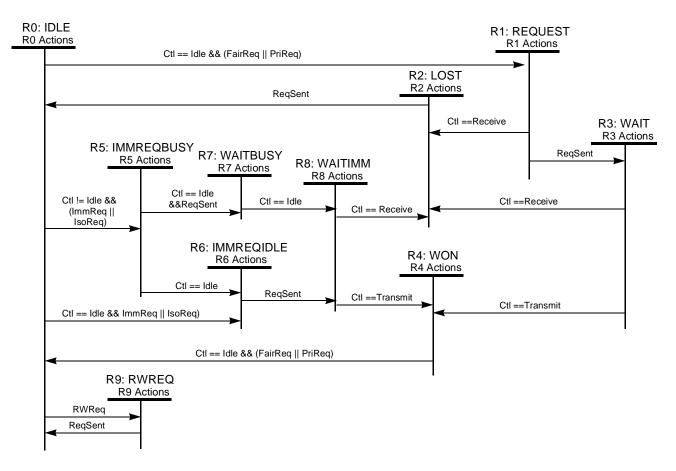

| Figure 5-10 — Link request state machine                                           |    |

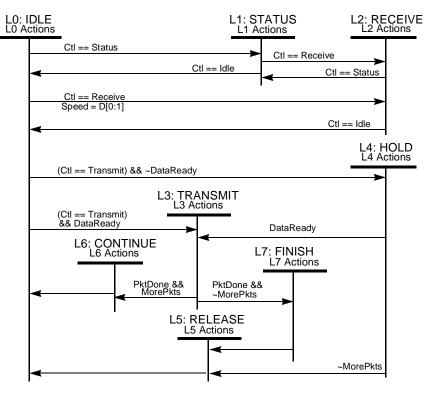

| Figure 5-10 — Link general state diagram                                           |    |

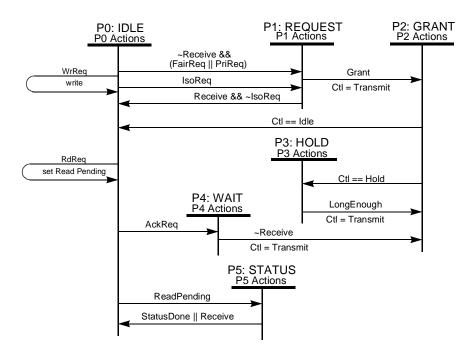

| Figure 5-12 — PHY general state diagram                                            |    |

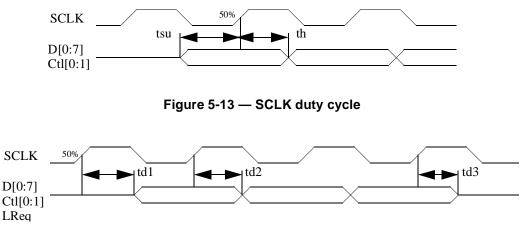

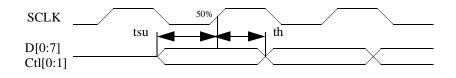

| Figure 5-12 — SCLK duty cycle                                                      |    |

| Figure 5-14 — Link to PHY transfer waveform                                        |    |

| Figure 5-15— PHY to link transfer waveform                                         |    |

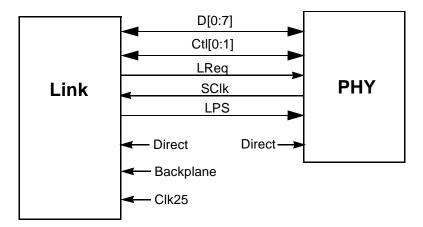

| Figure 6-1 — Self-ID packet format                                                 |    |

| Figure 6-2 — Link-on packet format                                                 |    |

| Figure 6-2 — PHY configuration packet format                                       |    |

| Figure 6-4 — Ping packet format                                                    |    |

| Figure 6-5 — Cable physical layer architecture                                     |    |

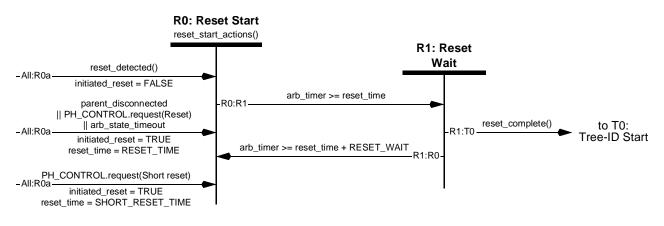

| Figure 6-6 — Bus reset state machine                                               |    |

|                                                                                    |    |

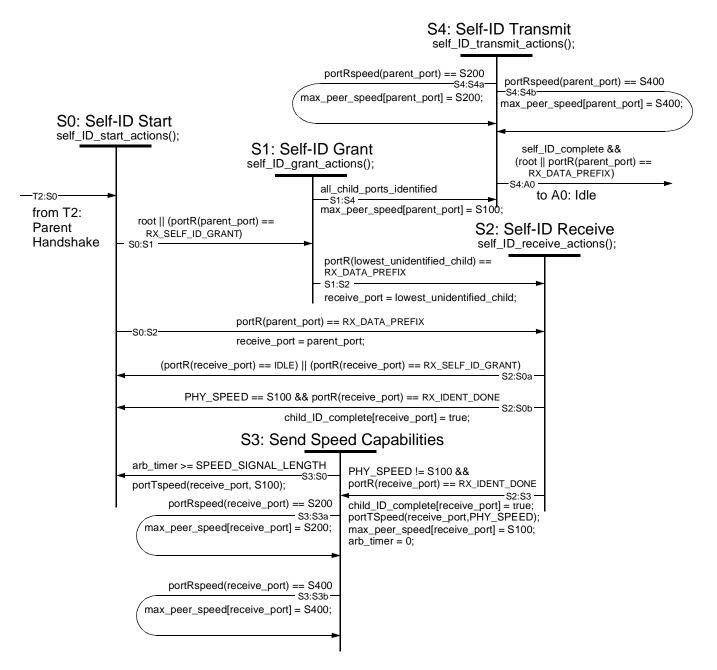

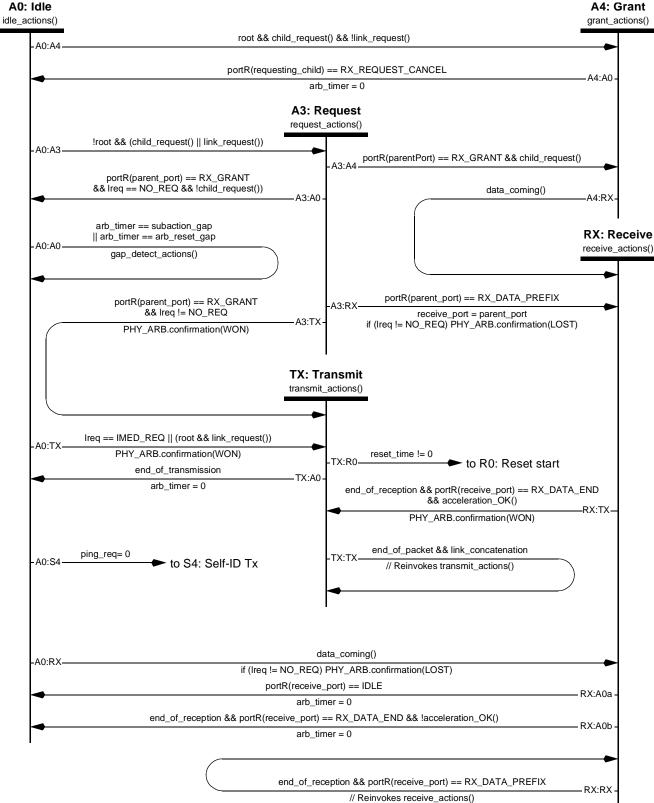

| Figure 6-7 — Self-ID state machine<br>Figure 6-8 — Cable arbitration state machine |    |

|                                                                                    |    |

| Figure 6-9 — Port disable logic<br>Figure 7-1 — OUTPUT_MASTER_PLUG format          |    |

| <b>č</b>                                                                           |    |

| Figure 7-2 — OUTPUT_PLUG format                                                    |    |

| Figure 7-3 — INPUT_MASTER_PLUG format                                              |    |

| Figure 7-4 — INPUT_PLUG format                                                     |    |

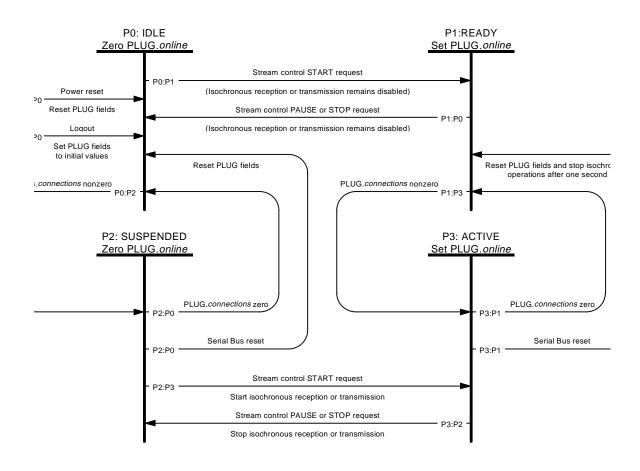

| Figure 7-5 — Plug state transitions                                                | 93 |

| Table 1-1— Size notation examples                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1-2— Specific expression summary                                                                                                 | 5  |

| Table 1-3— Serial Bus data types                                                                                                       | 6  |

| Table 1-4— Example CSR addressing conventions                                                                                          |    |

| Table 1-5— Register definition fields                                                                                                  | 8  |

| Table 1-6— Read value fields                                                                                                           | 8  |

| Table 1-7— Write value fields                                                                                                          | 8  |

| Table 4-1 — Connector socket signal assignment                                                                                         |    |

| Table 4-2 — Performance group A                                                                                                        |    |

| Table 4-3 — Performance group B                                                                                                        |    |

| Table 4-4 — Performance group C                                                                                                        |    |

| Table 4-5 — Performance group D                                                                                                        |    |

| Table 4-6 — Performance group E                                                                                                        |    |

| Table 4-7 — Performance group F                                                                                                        |    |

| Table 4-8 — Performance group G                                                                                                        |    |

| Table 5-1 — Signal description                                                                                                         |    |

| Table 5-2 — Ctl[0:1] when PHY is driving                                                                                               |    |

| Table 5-3 — Ctl[0:1] when the Link is driving (upon a grant from the PHY)                                                              |    |

| Table 5-4 — Bus request format for cable environment                                                                                   |    |

| Table 5-5 — Bus request format for backplane environment                                                                               |    |

| Table 5-6 — Read request format                                                                                                        |    |

| Table 5-7 — Write request format                                                                                                       |    |

| Table 5-8 — Request type field                                                                                                         |    |

| Table 5-9 — Request speed field                                                                                                        |    |

| Table 5-10 — Status bits                                                                                                               |    |

| Table 5-11 — Receive speed code                                                                                                        |    |

| Table 5-12 — Legacy PHY register fields for the cable environment                                                                      |    |

| Table 5-12     Degacy III register fields for the cable environment       Table 5-13     PHY register fields for the cable environment |    |

| Table 5-14 — PHY register Port Status page fields                                                                                      | 50 |

| Table 5-15 — PHY register fields for the backplane environment                                                                         |    |

| Table 5-16 — Link request state machine inputs                                                                                         | 52 |

| Table 5-17 — Link request state machine outputs                                                                                        |    |

| Table 5-18 — Link request state machine state definitions                                                                              |    |

| Table 5-19 — Link general state machine inputs                                                                                         |    |

| Table 5-20 — Link general state machine outputs                                                                                        |    |

| Table 5-20     Ennk general state machine outputs       Table 5-21     Link general state definitions                                  |    |

| Table 5-21 — Phy general state definitions       Table 5-22 — PHY general state machine inputs                                         |    |

| Table 5-22 — PHY general state machine outputs         Table 5-23 — PHY general state machine outputs                                  |    |

| Table 5-23 — FITT general state machine outputs       Table 5-24 — PHY general state definitions                                       |    |

| Table 5-24 — ITTT general state definitions       Table 5-25 — AC timing parameters                                                    |    |

| Table 5-25 — Ac timing parameters       Table 6-1 — Self-ID packet fields                                                              |    |

| Table 6-2 — Link-on packet fields                                                                                                      |    |

| Table 6-2 — Efficient packet fields                                                                                                    |    |

| Table 6-3 — Fiff configuration packet fields                                                                                           |    |

| Table 6-5 — Cable PHY timing constants                                                                                                 |    |

|                                                                                                                                        |    |

| Table 6-6 — Cable PHY packet definitions         Table 6-7 — Cable PHY code definitions                                                |    |

| Table 6-7 — Cable PH F code definitions                                                                                                |    |

| Table 6-8 — Bus reset actions and conditions                                                                                           |    |

|                                                                                                                                        |    |

| Table 6-10 — Normal arbitration actions and conditions                                                                                 |    |

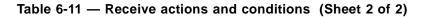

| Table 6-11 — Receive actions and conditions                                                                                            |    |

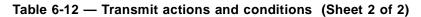

| Table 6-12 — Transmit actions and conditions                                                                                           |    |

| Table 7-1 — Plug control registers         Table 7-2 — Speed encoding                                                                  |    |

| Table 7-2 — Speed encoding         Table 7-2 — Entended encoding                                                                       |    |

| Table 7-3 — Extended speed encoding                                                                                                    |    |

| Table 9-1— | Serial Bus-dependent registers in initial | units space |  |

|------------|-------------------------------------------|-------------|--|

| Table 9-2— | Response code encoding                    |             |  |

# P1394a Draft Standard for a High Performance Serial Bus (Supplement)

### 1. Overview

### 1.1 Scope

This is a full-use standard whose scope is to provide a supplement to IEEE Std 1394-1995 that defines or clarifies features and mechanisms that facilitate management of Serial Bus resources, at reconfiguration or during normal operation, and that defines alternate cables and connectors that may be needed for specialized applications.

The following are included in this supplement:

- a) Cables and connectors for a 4-pin variant (from the 6-pin already standardized);

- b) Standardization of the PHY/LINK interface, which at present is an informative annex to the existing standard;

- c) A connection management protocol, and the necessary CSR facilities, for isochronous data;

- d) Performance enhancements to the PHY layer that are interoperable with the existing standard, *e.g.*, a method to shorten the arbitration delay when the last observed Serial Bus activity is an acknowledge packet;

- e) An incremental reconfiguration protocol, invoked when a device is connected to or disconnected from Serial Bus, which is designed to limit the circumstances under which a Serial Bus reset is necessary;

- f) A technique for Serial Bus topologies that form a physical loop to be resolved into a logical tree structure (required by the existing standard) without user intervention;

- g) Minor corrigenda to the existing standard.

The preceding are arranged in no particular order.

### 1.2 Purpose

Experience with Serial Bus has revealed some areas in which additional features or improvements may result in better performance or usability. This supplement to IEEE Std 1394-1995 reflects their consideration by a variety of users and their refinement into generally useful facilities or features.

### 1.3 References

This standard shall be used in conjunction with the following publications. When the following publications are superseded by an approved revision, the revision shall apply.

ANSI/EIA-364-B-90, Electrical Connector Test Procedures Including Environmental Classifications.<sup>1</sup>

IEEE Std 896.2-1991, IEEE Standard for Futurebus+<sup>®</sup>—Physical Layer and Profile Specification (ANSI).<sup>2</sup>

ISO/IEC 9899: 1990, Programming languages-C.<sup>3</sup>

ISO/IEC 13213: 1994 [ANSI/IEEE Std 1212, 1994 Edition], Information technology—Microprocessor systems—Control and Status Registers (CSR) Architecture for microcomputer buses.

### 1.4 Document organization

This standard contains this overview, a list of definitions, an informative summary description, sections of technical specification and application annexes. The new reader should read the informative summary and the sections that precede it before the remainder of the document.

### 1.5 Service model

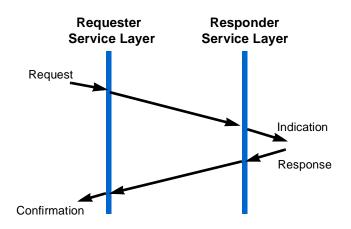

IEEE Std 1394-1995 and this supplement both use a protocol model with multiple layers. Each layer provides services to communicate with the next higher layer and with the Serial Bus management layer. These services are abstractions of a possible implementation; an actual implementation may be significantly different and still meet all the requirements. The method by which these services are communicated between the layers is not defined by this standard. Four types of service are defined by this standard:

- a) *Request service*. A request service is a communication from the higher layer to the lower layer to request the lower layer to perform some action. A request may also communicate parameters that may or may not be associated with an action. A request may or may not be confirmed by a confirmation. A data transfer request usually will trigger a corresponding indication on a peer node(s). (Since broadcast addressing is supported on the Serial Bus, it is possible for the request to trigger a corresponding indication on multiple nodes.)

- b) *Indication service*. An indication service is a communication from the lower layer to the upper layer to indicate a change of state or other event detected by the lower layer. An indication may also communicate parameters that are associated with the change of state or event. An indication may or may not be responded to by a response. A data transfer indication is originally caused by corresponding requests on a peer node.

- c) *Response service*. A response service is a communication from the higher layer to the lower layer to respond to an indication. A response may also communicate parameters that indicate the type of response to the indication. A response is always associated with an indication. A data transfer response usually will trigger a corresponding confirmation on a peer node.

- d) *Confirmation service*. A confirmation service is a communication from the lower layer to the upper layer to confirm a request service. A confirmation may also communicate parameters that indicate the completion status of the request or any other status. A confirmation is always associated with a request. For data transfer requests, the confirmation may be caused by a corresponding response on a peer node.

<sup>&</sup>lt;sup>1</sup> EIA publications are available from Global Engineering, 1990 M Street NW, Suite 400, Washington, DC, 20036, USA.

<sup>&</sup>lt;sup>2</sup> IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA.

<sup>&</sup>lt;sup>3</sup> ISO/IEC publications are available from the ISO Central Secretariat, Case Postale 56, 1 rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse. ISO publications are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

If all four service types exist, they are related as shown by the following figure:

Figure 1-1—Service model

# **1.6 Document notation**

### 1.6.1 Mechanical notation

All mechanical drawings in this document use millimeters as the standard unit and follow ANSI Y14.2 and ANSI Y14.5-1982 formats.

### 1.6.2 Signal naming

All electrical signals are shown in all uppercase characters and active-low signals have the suffix "\*". For example: TPA and TPA\* are the normal and inverted signals in a differential pair.

### 1.6.3 Size notation

The Serial Bus description avoids the confusing terms word, half-word and double-word, which have widely different definitions depending on the word size of the processor. In their place, the Serial Bus description uses terms established in previous IEEE bus standards, which are independent of the processor. These terms are illustrated in table 1-1.

| Size (in bits) | 16-bit word notation | 32-bit word notation | IEEE standard notation<br>(used in this standard) |

|----------------|----------------------|----------------------|---------------------------------------------------|

| 8              | byte                 | byte                 | byte                                              |

| 16             | word                 | half-word            | doublet                                           |

| 32             | long-word            | word                 | quadlet                                           |

| 64             | quad-word            | double               | octlet                                            |

Table 1-1—Size notation examples

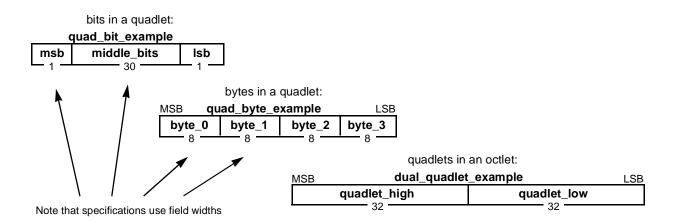

The Serial Bus uses big-endian ordering for byte addresses within a quadlet and quadlet addresses within an octlet. For 32-bit quadlet registers, byte 0 is always the most significant byte of the register. For a 64-bit quadlet-register pair, the first quadlet is always the most significant. The field on the left (most significant) is transmitted first; within a field the most significant bit is also transmitted first. This ordering convention is illustrated in figure 1-2.

Figure 1-2—Bit and byte ordering

Although Serial Bus addresses are defined to be big-endian, their data values may also be processed by little-endian processors. To minimize the confusion between conflicting notations, the location and size of bit fields are usually specified by width, rather than their absolute positions, as is also illustrated in figure 1-2.

When specific bit fields must be used, the CSR Architecture convention of consistent big-endian numbering is used. Hence, the most significant bit of a quadlet ("msb" in figure 1-2) will be labeled "quad\_bit\_example[0]," the most significant byte of a quadlet ("byte\_0") will be labeled "quad\_byte\_example[0:7]," and the most significant quadlet in an octlet ("quadlet\_high") will be labeled "dual\_quadlet\_example[0:31]."

The most significant bit shall be transmitted first for all fields and values defined by this standard, including the data values read or written to control and status registers (CSRs).

### 1.6.4 Numerical values

Decimal, hexadecimal and binary numbers are used within this document. For clarity, the decimal numbers are generally used to represent counts, hexadecimal numbers are used to represent addresses and binary numbers are used to describe bit patterns within binary fields.

Decimal numbers are represented in their standard 0, 1, 2,... format. Hexadecimal numbers are represented by a string of one or more hexadecimal (0-9, A-F) digits followed by the subscript 16. Binary numbers are represented by a string of one or more binary (0,1) digits, followed by the subscript 2. Thus the decimal number "26" may also be represented as " $1A_{16}$ " or " $11010_2$ ". In C code examples, hexadecimal numbers have a "0x" prefix and binary numbers have a "0b" prefix, so the decimal number "26" would be represented by "0x1A" or "0b11010."

# 1.6.5 Packet formats

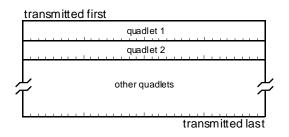

Serial Bus packets consist of a sequence of quadlets. Packet formats are shown using the style given in figure 1-3.

Figure 1-3—Example packet format

Fields appear in packet formats with their correct position and widths. Field widths are also stated explicitly in field descriptions. Bits in a packet are transmitted starting with the upper leftmost bit and finishing with the bottom rightmost bit. Given the rules in 1.6.3, this means that all fields defined in this standard are sent most significant bit first.

# 1.6.6 Register formats

All Serial Bus registers are documented in the style used by the CSR Architecture.

# 1.6.7 C code notation

The conditions and actions of the state machines are formally defined by C code. Since many C code operators are not obvious to the casual reader, their meanings are summarized in table 1-2.

| Expression | Description                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------|

| ~I         | Bitwise complement of integer I                                                                             |

| ++I        | Pre-increment of integer I (I is incremented, then used in the expression)                                  |

| I          | Pre-decrement of integer I (I is decremented, then used in the expression)                                  |

| I^J        | Bitwise XOR of integers I and J                                                                             |

| I&J        | Bitwise AND of integer values I and J                                                                       |

| I   J      | Bitwise OR of integer values I and J                                                                        |

| I << J     | Value of I, shifted left by J bits, zero fill                                                               |

| I >> J     | Value of I, shifted right by J bits, zero fill if I is an unsigned number,<br>sign extension if I is signed |

| I == J     | Equality test, true if I is equal to J                                                                      |

| I != J     | Inequality test, true if I is not equal to J                                                                |

| !B         | Logical negation of boolean variable B                                                                      |

| A && B     | Logical AND of boolean values A and B                                                                       |

| А    В     | Logical OR of boolean values A and B                                                                        |

In addition, the nonstandard data types (actually, object classes) listed in table 1-3 are supported.

Table 1-3—Serial Bus data types

| Data type | Description                                                                  |  |

|-----------|------------------------------------------------------------------------------|--|

| timer     | real value (units of seconds) that autonomously increments at a defined rate |  |

| boolean   | One bit value where 1 is true and 0 is false                                 |  |

Other, more specific data types are defined in the clauses where they are relevant.

All C code is executed as if it takes zero time. Time only elapses when the following function is called ("time" is in units of seconds):

void wait (real time); // wait for "time" to elapse

### 1.6.8 State machine notation

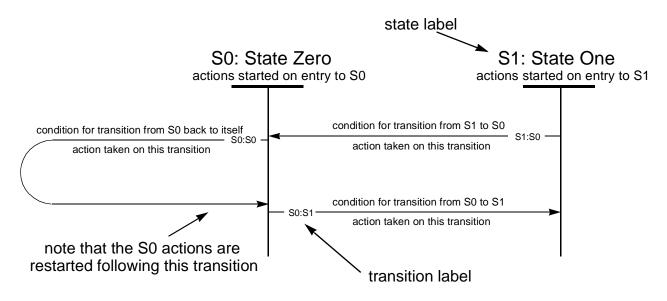

All state machines in this standard use the style shown in figure 1-4.

Figure 1-4—State machine example

These state machines make three assumptions:

- a) Time elapses only within discrete states.

- b) State transitions are logically instantaneous, so the only actions taken during a transition are setting flags and variables and sending signals.

- c) Every time a state is entered, the actions of that state are started. Note that this means that a transition that points back to the same state will restart the actions from the beginning.

#### 1.6.9 CSR, ROM and field notation

This standard describes a number of CSRs and fields within these registers. To distinguish register and field names from node states or descriptive text, the register name is always capitalized. Thus, the notation STATE\_CLEAR.*lost* is used to describe the lost bit within the STATE\_CLEAR register. In this standard, a bold type font is used to emphasize a term, particularly on its first usage.

All CSRs are quadlets and are quadlet aligned. The address of a register (which is always a multiple of 4) is specified as the byte offset from the beginning of the initial register space. When a range of register addresses is described, the ending address is the address of the last register, which is also a multiple of 4. These addressing conventions are illustrated in table 1-4.

| Offset | Register Name   | Description              |  |

|--------|-----------------|--------------------------|--|

| 0      | STATE_CLEAR     | First CSR location       |  |

| 4-12   | OTHER_REGISTERS | Next three CSR locations |  |

| Table 1-4—Example CS | R addressing conventions |

|----------------------|--------------------------|

|----------------------|--------------------------|

This document describes a number of configuration ROM entries and fields within these entries. To distinguish ROM entry and field names from node states or descriptive text, the first character of the entry name is always capitalized. Thus, the notation Bus\_Info\_Block.cmc is used to describe the cmc bit within the Bus\_Info\_Block entry.

Entries within temporary data structures, such as packets, timers and counters, are shown in lowercase (following normal C language conventions) and are formatted in a fixed-space typeface. Examples are arb\_timer and connected[i].

NOTE—Within the C code, the character formatting is not used, but the capitalization rules are followed.

# 1.6.10 Register specification format

This document precisely defines the format and function of Serial Bus-specific CSRs. Some of these registers are readonly, some are read-write and some have special side-effects on writes. To define the content and function of these CSRs wholly, their specification includes the format (the sizes and names of bit field locations), the initial value of the register (if not zero), the value returned when the register is read and the effect(s) when the register is written. An example register is illustrated in figure 1-5.

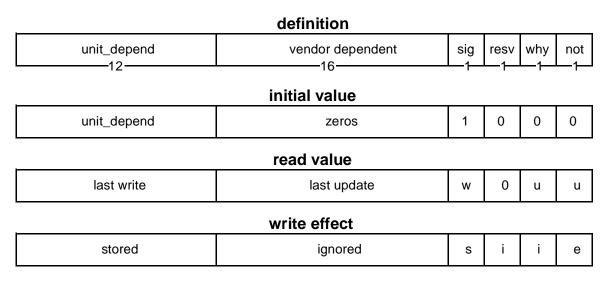

Figure 1-5—CSR format specification (example)

The register definition lists the names of register fields. These names are descriptive, but the fields are defined in the text; their function should not be inferred solely from their names. However, the register definition fields in table 1-5 have generic meanings.

| Table 1-5—Register | definition | fields |

|--------------------|------------|--------|

|--------------------|------------|--------|

| Name             | Abbreviation  | Definition                                                                                                                                                            |

|------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| unit dependent   | unit_depend   | The meaning of this field shall be defined by the unit architecture(s) of the node.                                                                                   |

| vendor dependent | vendor_depend | The meaning of this field shall be defined by the vendor of the node.<br>Within a unit architecture, the unit_dependent fields may be defined to be vendor dependent. |

The CSRs defined in this document shall be initialized when power is restored (a **power\_reset**) or when a quadlet is written to its RESET\_START register (a **command\_reset**). For most registers, the initial value after a power\_reset or command\_reset is the same. When the initial CSR values differ, the two initial values are explicitly illustrated.

The read value fields in table 1-6 have a generic meaning.

Table 1-6—Read value fields

| Name        | Abbreviation | Definition                                                                                               |

|-------------|--------------|----------------------------------------------------------------------------------------------------------|

| last write  | W            | The value of the data field shall be the value that was previously written to the same register address. |

| last update | u            | The value of the data field shall be the last value that was updated by node hardware.                   |

The write-effect fields in table 1-7 have a generic meaning.

Table 1-7—Write value fields

| Name    | Abbreviation | Definition                                                                                                                                |  |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| stored  | S            | The value of the written data field shall be immediately visible to reads of the same register.                                           |  |

| ignored | i            | The value of the written data field shall be ignored; it shall have no effect on the state of the node.                                   |  |

| effect  | e            | The value of the written data field shall have an effect on the state of the node, but immediately visible to reads of the same register. |  |

The register description specifies its bus transaction read/write characteristics, as well as whether it is a required register. A read-write register ( $\mathbf{RW}$ ) is expected to be read and written via bus transactions; a read-only register ( $\mathbf{RO}$ ) is expected to only be read; a write-only register ( $\mathbf{WO}$ ) is expected to only be written. Although reads of WO registers and writes of RO registers are not expected, the register definition still defines their results.

# 1.6.11 Reserved registers and fields

Some CSR addresses correspond to unimplemented registers. This includes optional registers (when the option is not implemented) and reserved registers (which are required to be unimplemented). The capabilities of these unimplemented registers are exactly defined to minimize conflicts between current implementations and future definitions, as illustrated in figure 1-6.

| definition            |  |  |

|-----------------------|--|--|

| unimplemented         |  |  |

| 32                    |  |  |

| initial value         |  |  |

| zeros                 |  |  |

| read value            |  |  |

|                       |  |  |

| zeros                 |  |  |

| zeros<br>write effect |  |  |

#### Figure 1-6—Reserved fields

Within an implemented register, a field that is reserved for future revisions of this standard is labeled *reserved* (sometimes abbreviated as r or *resv*). For a reserved field within an implemented register, the field is ignored on a write and returns zero on a read, as formally specified below:

#### reserved:

| Required.      | Reserved for future definitions. |

|----------------|----------------------------------|

| Initial value: | Zero.                            |

| Read4 value:   | Shall return zero.               |

| Write4 effect: | Shall be ignored.                |

### 1.6.12 Operation description priorities

The description of operations in this standard are done in three ways: state machines, C code segments and English language. If more than one description is present, then priority shall be given first to the state machines, then the C code segments and finally to the English text (including the state machine notes).

# 2. Definitions and abbreviations

# 2.1 Conformance glossary

Several keywords are used to differentiate between different levels of requirements and optionality, as follows:

**2.1.1 expected:** A keyword used to describe the behavior of the hardware or software in the design models assumed by this standard. Other hardware and software design models may also be implemented.

2.1.2 ignored: A keyword that describes bits, bytes, quadlets, octlets or fields whose values are not checked by the recipient.

**2.1.3 may:** A keyword that indicates flexibility of choice with no implied preference.

**2.1.4 reserved:** A keyword used to describe objects—bits, bytes, quadlets, octlets and fields—or the code values assigned to these objects in cases where either the object or the code value is set aside for future standardization. Usage and interpretation may be specified by future extensions to this or other standards. A reserved object shall be zeroed or, upon development of a future standard, set to a value specified by such a standard. The recipient of a reserved object shall not check its value. The recipient of a defined object shall check its value and reject reserved code values.

**2.1.5 shall:** A keyword indicating a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products conforming to this standard.

**2.1.6 should:** A keyword indicating flexibility of choice with a strongly preferred alternative. Equivalent to the phrase "is recommended."

# 2.2 Technical glossary

The following are terms that are used within this standard:

2.2.1 acknowledge: An acknowledge packet.

2.2.2 acknowledge gap: The period of idle bus between the end of a packet and the start of an acknowledge.

**2.2.3 acknowledge packet:** A link-layer packet returned by a destination node back to a source node in response to most primary packets. An acknowledge packet is always exactly 8 bits long.

**2.2.4 arbitration:** The process by which nodes compete for ownership of the bus. The cable environment uses a hierarchical point-to-point algorithm, while the backplane environment uses the bit-serial process of transmitting an arbitration sequence. At the completion of an arbitration contest, only one node will be able to transmit a data packet.

**2.2.5 arbitration clock rate:** The rate used to define a number of timing requirements within the backplane physical layer. It is  $49.152 \text{ MHz} \pm 100 \text{ ppm}$ , regardless of the backplane interface technology.

**2.2.6 arbitration reset gap:** The minimum period of idle bus that has to occur after a source using the fairness protocol has won an arbitration contest before it can once again compete for bus mastership. This is longer than a normal subaction gap.

**2.2.7 arbitration sequence:** For the backplane environment, a set of bits transmitted by nodes that wish to transmit packets that is used to determine which node will be able to transmit next.

**2.2.8 arbitration signal:** Bidirectional signal exchanged between nodes during arbitration. One of the PDUs for the physical layer (the other is the data bit).

**2.2.9 asynchronous packet:** A primary packet that contains the bus ID of the destination in the first quadlet. It is sent as the request subaction and/or response subaction of a transaction.

2.2.10 attached peer PHY: A peer cable PHY at the other end of a particular physical connection from the local PHY.

**2.2.11 base rate:** The lowest data rate used by Serial Bus in a particular cable environment. In multiple speed environments, all nodes have to be able to receive and transmit at the base rate. The base rate for the cable environment is  $98.304 \text{ MHz} \pm 100 \text{ ppm}$ .

**2.2.12 broadcast physical ID:** A physical ID with a value of 111111<sub>2</sub>.

2.2.13 bus ID: A 10-bit number uniquely specifying a particular bus within a system of multiple interconnected buses.

**2.2.14 bus manager:** The node that provides advanced power management, optimizes Serial Bus performance, describes the topology of the bus and cross-references the maximum speed for data transmission between any two nodes on the bus. The bus manager node may also be the isochronous resource manager node.

2.2.15 byte: Eight bits of data.

**2.2.16 cable physical layer**: The version of the physical layer applicable to the Serial Bus cable environment.

2.2.17 cable PHY: Abbreviation for the cable physical layer.

**2.2.18 concatenated transaction:** A transaction where the request and response subactions are directly concatenated without a gap between the acknowledge of the request and the response packet.

2.2.19 connected PHY: A peer cable PHY at the other end of a particular physical connection from the local PHY.

**2.2.20 CSR** Architecture: ISO/IEC 13213: 1994 [ANSI/IEEE Std 1212, 1994 Edition], Information technology—Micro-processor systems—Control and Status Registers (CSR) Architecture for microcomputer buses.

**2.2.21 cycle master:** The node that generates the periodic cycle start.

2.2.22 cycle start: A primary packet sent by the cycle master that indicates the start of an isochronous cycle.

**2.2.23 data bit:** The smallest signaling element used by the physical layer for transmission of packet data on the medium. One of the PDU's for the physical layer (the other is the arbitration signal).

**2.2.24 destination**: A node that is addressed by a packet. If the destination is individually addressed by a source, then it has to return an acknowledge packet.

2.2.25 doublet: Two bytes, or 16 bits, of data.

**2.2.26 dribble bits:** Extra bits added to the end of a packet that allow extra synchronization in implementations.

**2.2.27 fairness interval:** A group of back-to-back transfers during which each competing source using the fairness protocol gets a single transfer. The delimiters of the fairness interval are arbitration reset gaps.

**2.2.28 gap:** A period of idle bus.

**2.2.29 initial node space:** The 256 terabytes of Serial Bus address space that is available to each node. Addresses within initial node space are 48 bits and are based at zero. The initial node space includes initial memory space, private space, initial register space and initial units space. See either ISO/IEC 13213:1994 or IEEE Std 1394-1995 for more information on address spaces.

**2.2.30 initial register space:** A two kilobyte portion of initial node space with a base address of FFFF F000 000016. This address space is reserved for resources accessible immediately after a bus reset. Core registers defined by ISO/IEC 13213:1994 are located within initial register space as are Serial Bus-dependent registers defined by IEEE Std 1394-1995.

**2.2.31 initial units space:** A portion of initial node space with a base address of FFFF F000 040016. This places initial units space adjacent to and above initial register space. The CSR's and other facilities defined by unit architectures are expected to lie within this space.

**2.2.32 isochronous:** The essential characteristic of a time-scale or a signal such that the time intervals between consecutive significant instances either have the same duration or durations that are integral multiples of the shortest duration.

**2.2.33 isochronous channel:** A relationship between a node that is the talker and one or more nodes that are listeners, identified by a channel number. One isochronous packet, identified by the channel number, may be sent by the talker during each isochronous cycle. Channel numbers are allocated cooperatively through isochronous resource management facilities.

**2.2.34 isochronous cycle:** An operating mode of the bus that begins after a cycle start is sent and ends when a subaction gap is detected. During an isochronous cycle, only isochronous subactions may occur. An isochronous cycle begins every 125  $\mu$ s, on average.

2.2.35 isochronous gap: The period of idle bus before the start of arbitration for an isochronous subaction.

**2.2.36 isochronous resource manager:** The node that contains the facilities needed to manage isochronous resources. In particular, the isochronous resource manager includes the BUS\_MANAGER\_ID, BANDWIDTH\_AVAILABLE and CHANNELS\_AVAILABLE registers. In addition, if there is no bus manager on the local bus, the isochronous resource manager may also perform limited power management and select a node to be the cycle master.

**2.2.37 isochronous subaction:** A complete link layer operation (arbitration and isochronous packet) that is sent only during an isochronous cycle.

**2.2.38 kilobyte:** A quantity of data equal to  $2^{10}$  bytes.

**2.2.39 link layer (LINK):** The layer, in a stack of three protocol layers defined for Serial Bus, that provides the service to the transaction layer of one-way data transfer with confirmation of reception. The link layer also provides addressing, data checking and data framing. The link layer also provides an isochronous data transfer service directly to the application.

2.2.40 LINK: Abbreviation for the link layer.

**2.2.41 listener:** A node that receives an isochronous subaction for an isochronous channel. There may be zero, one or more than one listeners for any given isochronous channel.

**2.2.42 local bus ID:** A bus ID with a value of 1111111111<sub>2</sub>.

**2.2.43 lock-request packet:** The packet transmitted during the request subaction portion of a lock transaction.

2.2.44 lock-response packet: The packet transmitted during the response subaction portion of a lock transaction.

**2.2.45 lock transaction:** A transaction that passes an address, subcommand and data parameter(s) from the requester to the responder and returns a data value from the responder to the requester. The subcommand specifies which indivisible update is performed at the responder; the returned data value is the previous value of the updated data.

2.2.46 module: The smallest component of physical management; i.e., a replaceable device.

**2.2.47 natural priority:** The order of packet transmission of a node given that all nodes start arbitration at the same instant using the same priority level. For the cable environment, the closer a node is to the root, the higher its natural priority. For the backplane environment, the priority level and node offset are concatenated to give its natural priority.

**2.2.48 node:** An addressable device attached to Serial Bus with at least the minimum set of control registers. Changing the control registers on one node does not affect the state of control registers on another node.

**2.2.49 node controller:** A component within a node that provides a coordination point for management functions exclusively local to a given node and involving the application, transaction, link and physical elements located at that node.

**2.2.50 node ID:** This is a unique 16-bit number, which distinguishes the node from other nodes in the system. The 10 most significant bits of node ID are the same for all nodes on the same bus; this is the bus ID. The six least-significant bits of node ID are unique for each node on the same bus; this is called the physical ID. The physical ID is uniquely assigned as a consequence of bus initialization.

**2.2.51 nonreturn to zero** (**NRZ**): A signaling technique in which a polarity level high represents a logical "1" (one) and a polarity level low represents a logical level "0" (zero).

2.2.52 octlet: Eight bytes, or 64 bits, of data.

**2.2.53 packet:** A serial stream of clocked data bits. A packet is normally the PDU for the link layer, although the cable physical layer can also generate and receive special short packets for management purposes.

2.2.54 path: The concatenation of all the physical links between the link layers of two nodes.

2.2.55 payload: The portion of a primary packet that contains data defined by an application layer.

**2.2.56 PCB**: Printed circuit board.

2.2.57 PDU: Abbreviation for protocol data unit.

**2.2.58 peer:** Service layer on a remote node at the same level. For instance a "peer link layer" is the link layer on a different node.

**2.2.59 PHY:** Abbreviation for the physical layer.

**2.2.60 PHY packet:** A packet either generated or received by the cable physical layer. These packets are always exactly 64 bits long where the last 32 bits are the bit complement of the first 32 bits.

**2.2.61 physical connection:** The full-duplex physical layer association between directly connected nodes. In the case of the cable physical layer, this is a pair of physical links running in opposite directions.

**2.2.62 physical ID:** The least-significant 6 bits of the node ID. This number is unique on a particular bus and is chosen by the physical layer during initialization.

**2.2.63 physical layer (PHY):** The layer, in a stack of three protocol layers defined for Serial Bus, that translates the logical symbols used by the link layer into electrical signals on the different Serial Bus media. The physical layer guarantees that only one node at a time is sending data and defines the mechanical interfaces for Serial Bus. There are different physical layers for the backplane and for the cable environment.

**2.2.64 physical link:** In the cable physical layer, the simplex path from the transmit function of the port of one node to the receive function of a port of a directly connected node.

**2.2.65 port:** A physical layer entity in a node that connects to either a cable or backplane and provides one end of a physical connection with another node.

**2.2.66 primary packet:** A packet made up of whole quadlets that contains a transaction code in the first quadlet. Any packet that is not an acknowledge or a PHY packet.

**2.2.67 protocol data unit (PDU):** Information delivered as a unit between peer entities that may contain control information, address information and data.

This is an unapproved standards draft, subject to change

2.2.68 quadlet: Four bytes, or 32 bits, of data.

2.2.69 quadlet aligned address: An address with zeros in the two least significant bits.

**2.2.70 register:** A term used to describe quadlet aligned addresses that may be read or written by Serial Bus transactions. In the context of this standard, the use of the term register does not imply a specific hardware implementation. For example, in the case of split transactions that permit sufficient time between the request and response subactions, the behavior of the register may be emulated by a processor within the module.

**2.2.71 request:** A subaction with a transaction code and optional data sent by a node (the requester) to another node (the responder).

**2.2.72 response:** A subaction sent by a node (the responder) that sends a response code and optional data back to another node (the requester).

**2.2.73 self-ID packet:** A special packet (see 4.3.4.1) sent by a cable PHY during the self-ID phase following a reset. One to four self-ID packets are sent by a given node depending on the maximum number of ports it has.

**2.2.74 Serial Bus management:** The set of protocols, services and operating procedures that monitors and controls the various Serial Bus layers: physical, link and transaction.

2.2.75 services: A set of capabilities provided by one protocol layer entity for use by a higher layer or by management entities.

2.2.76 service primitive: A specific service provided by a particular protocol layer entity.

2.2.77 source: A node that initiates a bus transfer.

**2.2.78 speed code:** The code used to indicate various bit rates for Serial Bus: S25 indicates 24.576 Mbps/s for TTL backplanes; S50 indicates 49.152 Mbps/s for BTL and ECL backplanes; S100 indicates the 98.304 Mbps/s base rate for cable; S200 and S400 indicate 196.608 Mbps/s and 393.216 Mbps/s for the cable.

**2.2.79 split transaction:** A transaction where the responder releases control of the bus after sending the acknowledge and then some time later starts arbitrating for the bus so it can start the response subaction. Other subactions may take place on the bus between the request and response subactions for the transaction.

**2.2.80 subaction gap:** The period of idle bus between subactions. There is no gap between the request and response subaction of a concatenated split transaction.

**2.2.81 subaction:** A complete link layer operation: arbitration, packet transmission and acknowledgment. The arbitration may be missing when a node already controls the bus and the acknowledge is not present for subactions with broadcast addresses or for isochronous subactions.

**2.2.82 talker:** A node that sends an isochronous subaction for an isochronous channel. There shall be no more than one talker for any given isochronous channel.

**2.2.83 terabyte:** A quantity of data equal to 2<sup>40</sup> bytes.

**2.2.84 transaction layer:** The layer, in a stack of three protocol layers defined for Serial Bus, that defines a request-response protocol to perform bus operations of type read, write and lock.

**2.2.85 transaction:** A request and the corresponding response. The response may be null for transactions with broadcast destination addresses. This is the PDU for the transaction layer.

2.2.86 unified transaction: A transaction that is completed in a single subaction.

**2.2.87 unit:** A component of a Serial Bus node that provides processing, memory, I/O or some other functionality. Once the node is initialized, the unit provides a CSR interface that is typically accessed by device driver software at an initiator. A node may have multiple units, which normally operate independently of each other.

**2.2.88 unit architecture:** The specification document that describes the interface to and the behaviors of a unit implemented within a node.

# 3. Summary description

Xxxx....

# 4. Alternative cable media attachment specification

The facilities of Serial Bus, IEEE Std 1394-1995, have found wide applicability in the consumer electronics industry for a new generation of digital products. For some of these product applications, the standard cable and connectors specified by the existing standard are less than ideal:

- Battery operated devices. Because these devices draw no power from the cable, their design could be simplified and their cost reduced if electrical isolation were not required for the connector assembly. In addition, the power conductors of the standard cable represent a potential source of analog noise—a significant concern for audio equipment.

- Hand-held devices. In contrast to the compactness of some consumer products, such as video camcorders, the standard cable and connectors are relatively bulky. A more compact design would be better suited to these products.

The alternative cables and conductors specified by this supplement enable backwards compatibility with the standard cables specified by IEEE Std 1394-1995. The remarks below apply to external (inter-crate) cabling, where extra care must be exercised for safety and EMC compliance. (Intra-crate connections are not standardized in this clause.)

With respect to these alternative cables and connectors, only, this section entirely replaces clause 4.2.1 of IEEE Std 1394-1995. Except as superseded by other sections in this supplement, (*e.g.*, clause 6., "Cable physical layer performance enhancement specifications,"), all other clauses in section 4 of the existing standard, "Cable physical layer specification," continue to apply to alternative cables and connectors.

# 4.1 Connectors

In typical applications computer, consumer electronic or peripheral equipment boxes shall present one or more connector sockets, for attachment to other boxes *via* cables. The detachable ends of the cable shall be terminated with connector plugs. IEEE Std 1394-1995 specifies standard connectors that have six contacts; this supplement specifies alternative connectors that have four contacts.

All dimensions, tolerances and descriptions of features which affect the intermateability of the alternative shielded connector plugs and sockets are specified within this clause. Features of connector plugs and sockets which do not affect intermateability are not specified and may vary at the option of the manufacturer. Connector features which are not directly controlled within this clause shall be indirectly controlled by performance requirements in clauses 4.3 and 4.4.

The holes and patterns (footprint) for the mounting of some of the possible versions of connectors to the printed circuit board (PCB) are recommended in clause 4.1.8

# 4.1.1 Connector plug

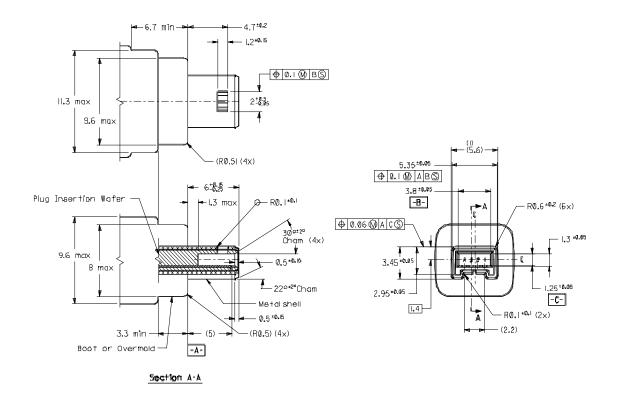

The mating features of the connector plug are specified in figures 4-1 and 4-2. They will assure the intermateability of the plug with the alternative sockets specified by this supplement.

It is recommended that the plug contacts have a cylindrical section in the contact area which makes contact at a right angle to the cylindrical section of the socket contacts, thus creating a "crossed cylinders" configuration. The contacts should be designed to create a Hertzian stress, (combination of cylindrical radius, normal force and base and surface material hardnesses) of 225,000-275,000 psi in the mating area. This is to assure that the low-energy signals used in this physical layer are transmitted through the non conductive films which are typically adsorbed on connector contacts.

NOTE—When a cable assembly plug is mated with a socket connector, there shall be 1.0 mm clearance, minimum, between the overmold on the assembly plug and the shield flange on the socket. This clearance is designed into the system to allow proper mating of both passive and latching cable plug assemblies. Deviation of this clearance may affect the performance of the connector interface.

Figures 4-1 and 4-2 describe a plug intended to be used when only detent retention with the socket is required.

Figure 4-1 — Plug body

Figure 4-2 — Plug section details

# 4.1.2 Connector plug terminations

The termination of the stranded wire to the plug contacts may be varied to suit the manufacturing process needs of the cable assembler.

For reference, the following methods are listed: crimp, insulation displacement (IDC), insulation piercing, welding and soldering

# 4.1.3 Connector socket

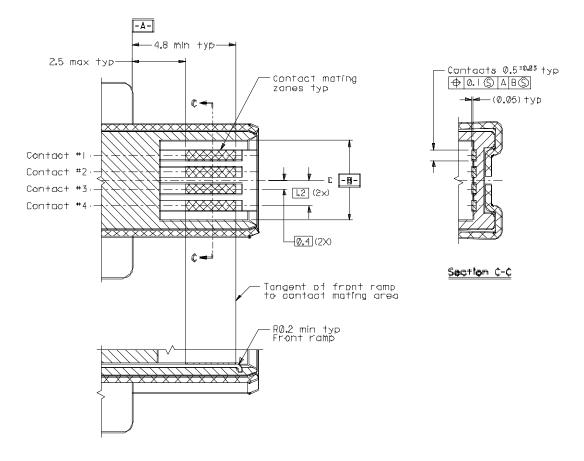

The mating features of the connector socket are described in figures 4-3 through 4-5. They will assure the intermateability of the socket with the alternative plugs specified by this supplement.

#### Figure 4-3 — Connector socket interface

The contacts are attached to the signals using the guidance in table 4-1.

| Table 4-1 — Connector socket signal assignment | Table 4-1 | - Connector | socket | signal | assignment |

|------------------------------------------------|-----------|-------------|--------|--------|------------|

|------------------------------------------------|-----------|-------------|--------|--------|------------|

| Contact number | Signal name | Comment                                                 |

|----------------|-------------|---------------------------------------------------------|

| 1              | TPB*        | Strobe on receive, data on transmit (differential pair) |

| 2              | TPB         |                                                         |

| 3              | TPA*        | Strobe on receive, data on transmit (differential pair) |

| 4              | TPA         |                                                         |

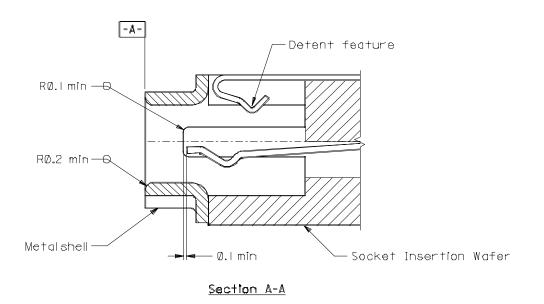

Figure 4-4 describes the relationship of the contacts and the shell. This includes the wiping portion of the contact and shell detent.

Figure 4-4 — Socket cross-section A-A

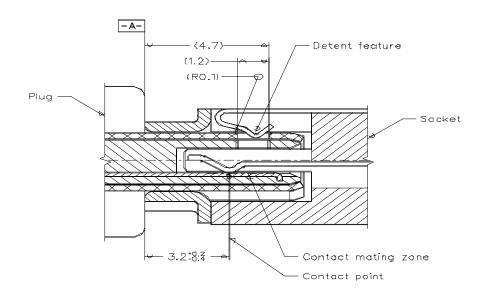

Figure 4-5 Shows the mated cross section of the plug and socket contacts.

Figure 4-5 — Cross-section of plug and socket contacts

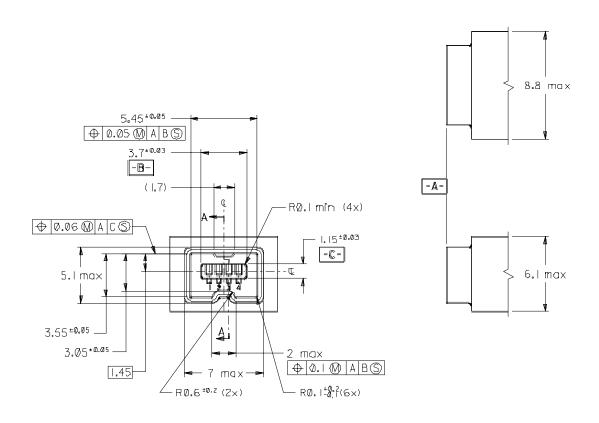

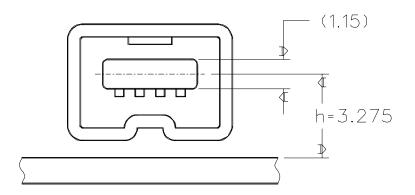

When mounted on a PCB, the socket shall be at a fixed height as illustrated by figure 4-6.

#### Figure 4-6 — Socket position when mounted on a PCB

#### 4.1.4 Contact finish on plug and socket contacts

It is necessary to standardize the electroplated finish on the contacts to assure the compatibility of plugs and sockets from different sources. The following standardized electroplatings are compatible and one shall be used on contacts.

- a) 0.76 µm (30µin), minimum, gold, over 1.27 µm (50 µin), minimum, nickel.

- b) 0.05 μm (2 μin), minimum, gold, over 0.76 μm (30 μin), minimum, palladium-nickel alloy (80% Pd-20% Ni), over 1.27 μm (50 μin), minimum, nickel.

#### NOTES:

1—Selective plating on contacts is acceptable. In that case, the above electroplating shall cover the complete area of contact, including the contact wipe area.

2—A copper strike is acceptable, under the nickel electroplate.

#### 4.1.5 Termination finish on plug and contact socket terminals

It is acceptable to use an electroplate of tin-lead with a minimum thickness of  $3.04 \ \mu m \ (120 \ \mu in)$  over  $1.27 \ \mu m \ (50 \ \mu in)$ , minimum, nickel. A copper strike is acceptable under the nickel.

#### 4.1.6 Shell finish on plugs and sockets

It is necessary to standardize the plated finish on the shells to insure compatibility of products from different sources. Both shells shall be electroplated with a minimum of  $3.03 \ \mu m$  (120  $\mu in$ ) of tin or tin alloy over a suitable barrier underplate.

### 4.1.7 Connector durability

The requirements of different end-use applications call for connectors which can be mated and unmated a different number of times, without degrading performance beyond acceptable limits. Accordingly, this supplement specifies minimum performance criteria of 1000 mating cycles.

# 4.1.8 PCB footprints

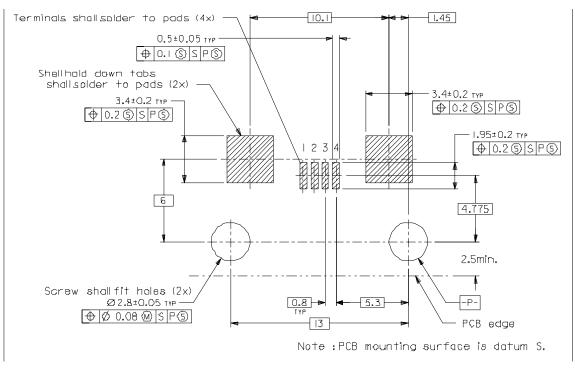

The footprint of a surface-mount PCB connector shall conform to the dimensional specifications illustrated by figure 4-7 below.

Figure 4-7 — Flat surface mount PCB connector footprint

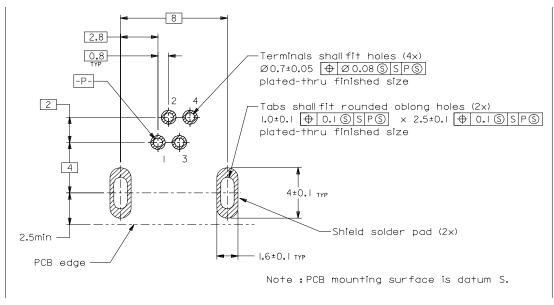

The footprint of a through-hole PCB connector shall conform to the dimensional specifications illustrated below.

Figure 4-8 — Flat through-hole mount PCB connector footprint

# 4.2 Cables

All cables and cable assemblies shall meet assembly criteria and test performance found in this supplement.

## 4.2.1 Cable material (reference)

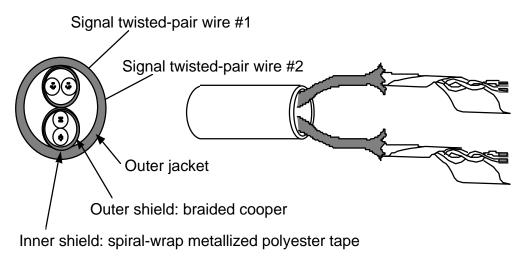

Linear cable material typically consists of two twisted pair conductors. The two twisted pairs carry the balanced differential data signals. Figure 4-9 <u>illustrates a reference design adequate</u> for a 4.5 m cable. Clause 4.4 describes the performance requirements for the cable assembly.

NOTE—This construction is illustrated *for reference only*; other constructions are acceptable as long as the performance criteria are met.

### 4.2.2 Cable assemblies

Cable assemblies consist of two plug connectors, either the standard connector specified by IEEE Std 1394-1995 or the alternative connector defined by this supplement, joined by a length of cable material. The suggested maximum length is 4.5 m. This is to assure that a maximally-configured cable environment does not exceed the length over which the end-to-end signal propagation delay would exceed the allowed time. Longer cable lengths are possible if special considerations is given to the actual Serial Bus system topology to be used, as discussed in greater detail in annex A of IEEE Std 1394-1995.

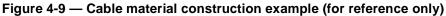

Both cable configurations, standard connector to standard connector and alternative connector to standard connector, are illustrated in the figures below. The connector pins are terminated as shown by figures 4-10 and 4-11. The two signal pairs "cross" in the cable to effect a transmit-to-receive interconnection.

# 4.3 Connector and cable assembly performance criteria

To verify the performance requirements, performance testing is specified according to the recommendations, test sequences and test procedures of ANSI/EIA 364-B-90. Table 1 of ANSI/EIA 364-B-90 shows operating class definitions for different end-use applications. For Serial Bus, the test specifications follow the recommendations for environmental class 1.3, which is defined as follows: "No air conditioning or humidity control with normal heating and ventilation." The

Equipment Operating Environmental Conditions shown, for class 1.3 in table 2 are: Temperature; +15 degree C to +85 degrees C, Humidity; 95% maximum., Class 1.3 is further described as operating in a "harsh environmental" state, but with no marine atmosphere.

Accordingly, the performance groupings, sequences within each group and the test procedures shall follow the recommendations of ANSI/EIA 364, except where the unique requirements of the Serial Bus connector and cable assembly may call for tests which are not covered in ANSI/EIA 364 or where the requirements deviate substantially from those in that document. In those cases, test procedures of other recognized authorities or specific procedures described in the annexes will be cited.

Sockets, plugs and cable assemblies shall perform to the requirements and pass all the following tests in the groups and sequences shown.

Testing may be done as follows:

- a) Plug and socket only. In this case, for those performance groups that require it, the plugs may be assembled to the cable, to provide a cable assembly, by the connector manufacturer or by a cable assembly supplier.

- b) Cable assembly (with a plug on each end) and socket. In this case, a single supplier may do performance testing for both elements or a connector supplier may team up with a cable assembly supplier to do performance testing as a team.

- c) Cable assembly only (with a plug on each end). In this case, the cable assembly supplier should use a plug connector source which has successfully passed performance testing, according to this standard.

- d) Plug only or socket only. In this case, the other half shall be procured from a source. which has successfully passed performance testing, according to this standard. For those performance groups that require it, the plugs may be assembled to the cable, to provide a cable assembly, by the connector manufacturer or by a cable assembly supplier.

#### NOTES:

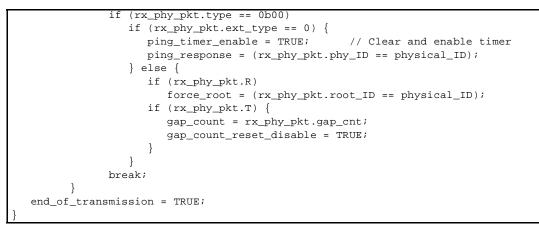

1—All performance testing is to be done with cable material which conforms to this specification. In order to test to these performance groups, ANSI/EIA tests require that the cable construction used be specified.